# Four Output Clock Generator/Jitter Cleaner With Integrated Dual VCOs

#### **FEATURES**

- Frequency Synthesizer With PLL/VCO and Partially Integrated Loop Filter

- Fully Configurable Outputs Including Frequency and Output Format

- Smart Input Multiplexer Automatically Switches Between one of two Reference Inputs.

- Multiple Operational Modes Include Clock Generation via Crystal, SERDES Startup Mode, Jitter Cleaning, and Oscillator Based Holdover Mode.

- Integrated EEPROM Determines Device Configuration at Power-up.

- Excellent Jitter Performance

- Integrated Frequency Synthesizer Including PLL, Multiple VCOs, and Loop Filter:

- Full Programmability Facilitates Phase Noise Performance Optimization Enabling Jitter Cleaner Mode

- Programmable Charge Pump Gain and Loop Filter Settings

- Unique Dual-VCO Architecture Supports a Wide Tuning Range 1.750 GHz – 2.356 GHz.

- Universal Output Blocks Support up to 2 Differential, 4 Single-Ended, or Combinations of Differential or Single-Ended:

- 0.5 ps RMS (10 kHz to 20 MHz) Output Jitter Performance

- Low Output Phase Noise: -130 dBc/Hz at 1 MHz offset, Fc = 491.52 MHz

- Output Frequency Ranges From 10.94

MHz to 1.175 GHz in Synthesizer Mode

- LVPECL, LVDS and LVCMOS

- Independent Output Dividers Support

Divide Ratios for

1,2,3,4,5,8,10,12,16,20,24 and 32.

- Flexible Inputs With Innovative Smart Multiplexer Feature:

- Two Universal Differential Inputs Accept Frequencies from 1 MHz up to 500 MHz (LVPECL), 500 MHz (LVDS), or 250 MHz (LVCMOS).

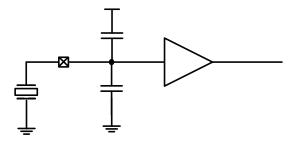

- One Auxiliary Input Accepts Single Ended Clock Source or Crystal. Auxiliary Input Accepts Crystals in the Range of 2MHz-42MHz or an LVCMOS Input up to 75MHz.

- Clock Generator Mode Using Crystal Input

- Smart Input Multiplexer can be Configured to Automatically Switch Between Highest Priority Clock Source Available Allowing for Fail-Safe Operation.

- Typical Power Consumption 750mW at 3.3V

- Integrated EEPROM Stores Default Settings;

Therefore, the Device can Power up in a Known, Predefined State.

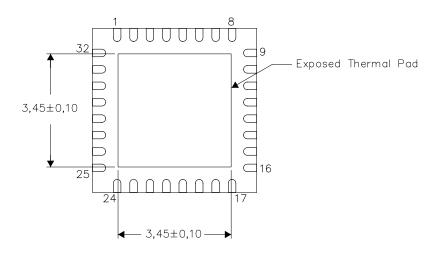

- Offered in QFN-32 Package

- ESD Protection Exceeds 2kV HBM

- Industrial Temperature Range –40°C to 85°C

## **APPLICATIONS**

- Data Converter and Data Aggregation Clocking

- Wireless Infrastructure

- Switches and Routers

- Medical Electronics

- Military and Aerospace

- Industrial

- Clock Generation and Jitter Cleaning

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### DESCRIPTION

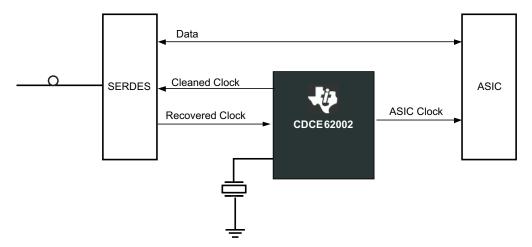

The CDCE62002 is a high performance clock generator featuring low output jitter, a high degree of configurability via a SPI interface, and programmable start up modes determined by on-chip EEPROM. Specifically tailored for clocking data converters and high-speed digital signals, the CDCE62002 achieves jitter performance under 0.5 ps RMS<sup>(1)</sup>. It incorporates a synthesizer block with partially integrated loop filter, a clock distribution block including programmable output formats, and an input block featuring an innovative smart multiplexer. The clock distribution block includes two individually programmable outputs that can be configured to provide different combinations of output formats (LVPECL, LVDS, LVCMOS). Each output can also be programmed to a unique output frequency (ranging from 10.94 MHz to 1.175 GHz<sup>(2)</sup>). If Both outputs are configured in single-ended mode (e.g., LVCMOS), the CDCE62002 supports up to four outputs. The input block includes one universal differential inputs which support frequencies up to 500 MHz and an auxiliary single ended input that can be connected to a CMOS level clock or configured to connect to an external AT-Cut crystal via an on board oscillator block. The smart input multiplexer has two modes of operation, manual and automatic. In manual mode, the user selects the synthesizer reference via the SPI interface. In automatic mode, the input multiplexer will automatically select between the highest priority input clock available.

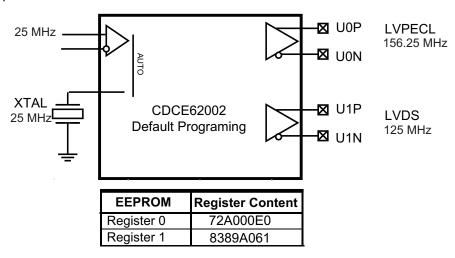

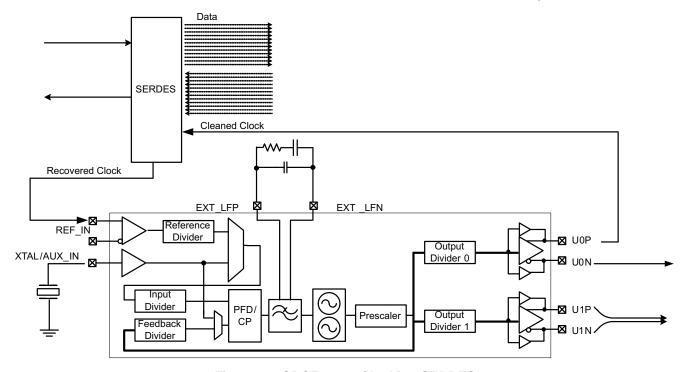

Figure 1. CDCE62002 Application Example

- (1) 10 kHz to 20 MHz integration bandwidth.

- (2) Frequency range depends on operational mode and output format selected.

## **DEVICE INFORMATION**

## **PIN FUNCTIONS**

## Table 1. CDCE62002 Pin Functions<sup>(1)</sup>

| PI                   | N           |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | QFN         | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCC_OUT0<br>VCC_OUT1 | 9,12 13,16  | Power    | 3.3V Supply for the Output Buffers. There is no internal connection between $V_{CC}$ and $AV_{CC}$ . It is recommended, that each $V_{CC}$ uses its own supply filter.                                                                                                                                                                                                                                                                                                       |

| VCC_PLLDIV           | 22          | Power    | 3.3V Supply Power for the PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC_PLLD             | 4           | Power    | 3.3V Supply Power for the PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC_PLLA             | 28          | A. Power | 3.3V Supply Power for the PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC_VCO              | 24          | A. Power | 3.3V Supply Power for the VCO Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC_IN               | 31          | Power    | 3.3V Supply Power for Input Buffer Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCC_AUX              | 1           | A. Power | 3.3V Supply Power for Crystal/Auxiliary Input Buffer Circuitry                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND_PLLDIV           | 21          | Ground   | Ground for PLL Divider circuitry. (short to GND)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND                  | PAD         | Ground   | Ground is on Thermal PAD. See Layout recommendation                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SPI_MISO             | 7           | OD       | 3-state LVCMOS Output that is enabled when SPI_LE is asserted low. It is the serial Data Output to the SPI bus interface.                                                                                                                                                                                                                                                                                                                                                    |

| SPI_LE               | 18          | I        | LVCMOS input, control Latch Enable for Serial Programmable Interface.  Note: The SPI_LE signal has to be high in order for the EEPROM to load correctly on the Rising edge of PD. The input has an internal 150-kΩ pull-up resistor                                                                                                                                                                                                                                          |

| SPI_CLK              | 17          | 1        | LVCMOS input, serial Control Clock Input for the SPI bus interface, with Hysteresis.                                                                                                                                                                                                                                                                                                                                                                                         |

| SPI_MOSI             | 8           | I        | LVCMOS input, Master Out Slave In as a serial Control Data Input to CDCE62002 for the SPI bus interface.                                                                                                                                                                                                                                                                                                                                                                     |

| PD                   | 6           | I        | PD or Power Down Pin is an active low pin and can be activated externally <b>or</b> via the corresponding Bit in SPI Register 2                                                                                                                                                                                                                                                                                                                                              |

|                      |             |          | In case of $\overline{PD}$ is asserted , the Device shuts Down and after $\overline{PD}$ goes high the EEPROM Loads into RAM and the VCO core re-starts calibration, PLL will try to relock and the Output dividers will get re-initiated. The LVPECL outputs are static low and high respectively and the LVCMOS outputs are all low or high if inverted. The input has an internal 150-k $\Omega$ pull-up resistor if left unconnected it will default to logic level "1". |

|                      |             |          | Note: The SPI_LE signal has to be high in order for the EEPROM to load correctly into RAM on the Rising edge of PD.                                                                                                                                                                                                                                                                                                                                                          |

| AUX_IN               | 2           | I        | Auxiliary Input is a Crystal input pin that connect to an internal oscillator circuitry. This input can also be driven by an LVCMOS signal.                                                                                                                                                                                                                                                                                                                                  |

|                      |             |          | This input also serves as the External Feedback Input that feeds directly to the PFD.                                                                                                                                                                                                                                                                                                                                                                                        |

| REF+                 | 29          | ļ        | Universal Input Buffer (LVPECL, LVDS, LVCMOS) positive input for the Reference Clock.                                                                                                                                                                                                                                                                                                                                                                                        |

| REF-                 | 30          | I        | Universal Input Buffer (LVPECL, LVDS,) negative input for the Reference Clock. In case of LVCMOS signaling pull-down this pin.                                                                                                                                                                                                                                                                                                                                               |

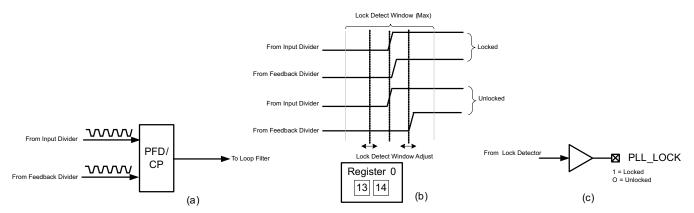

| PLL_LOCK             | 32          | 0        | PLL Lock indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TESTSYNC             | 19          | ı        | Test Point for Use for TI Internal SYNC Testing.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| REG_CAP1             | 5           | Analog   | Capacitor for the internal Regulator. Connect to a 10 μF Capacitor (Y5V)                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG_CAP2             | 27          | Analog   | Capacitor for the internal Regulator. Connect to a 10 μF Capacitor (Y5V)                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG_CAP3             | 20          | Analog   | Capacitor for the internal Regulator. Connect to a 10 μF Capacitor (Y5V)                                                                                                                                                                                                                                                                                                                                                                                                     |

| REG_CAP4             | 23          | Analog   | Capacitor for the internal Regulator. Connect to a 10 µF Capacitor (Y5V)                                                                                                                                                                                                                                                                                                                                                                                                     |

| VBB                  | 3           | Analog   | Capacitor for the internal termination Voltage. Connect to a 1 μF Capacitor (Y5V)                                                                                                                                                                                                                                                                                                                                                                                            |

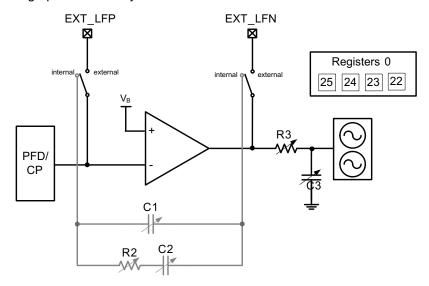

| EXT_LFP              | 25          | Analog   | External Loop Filter Input Positive                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EXT_LFN              | 26          | Analog   | External Loop Filter Input Negative.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| U0P:U0N<br>U1P:U1N   | 11,10 15,14 | 0        | The Main outputs of <b>CDCE62002</b> are user definable and can be any combination of up to 2 LVPECL outputs, 2 LVDS outputs or up to 4 LVCMOS outputs. The outputs are selectable via SPI interface. The power-up setting is EEPROM configurable.                                                                                                                                                                                                                           |

<sup>(1)</sup> NOTE: All VCC pins need to be connected for the device to operate properly.

#### **FUNCTIONAL DESCRIPTION**

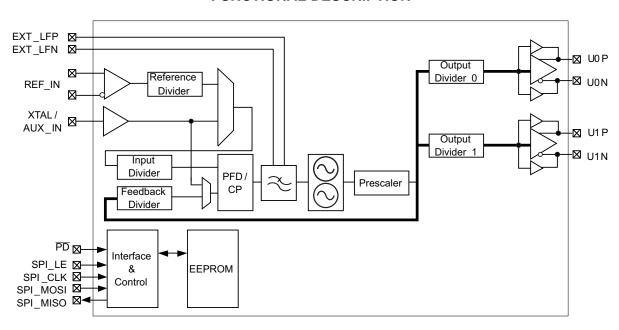

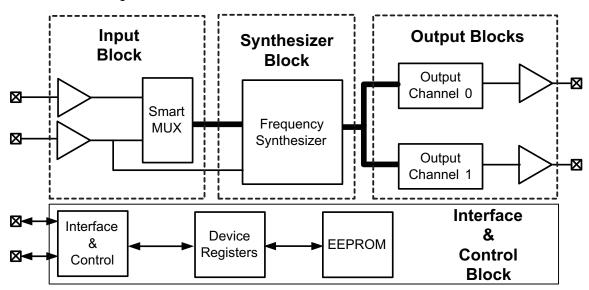

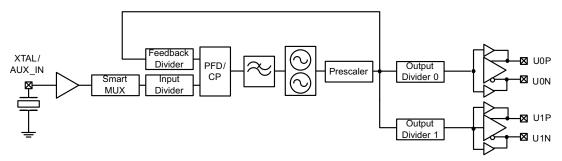

Figure 2. CDCE62002 Block Diagram

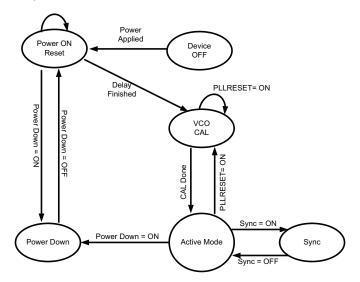

The CDCE62002 comprises of four primary blocks: the interface and control block, the input block, the output block, and the synthesizer block. In order to determine which settings are appropriate for any specific combination of input/output frequencies, a basic understanding of these blocks is required. The interface and control block determines the state of the CDCE62002 at power-up based on the contents of the on-board EEPROM. In addition to the EEPROM, the SPI port is available to configure the CDCE62002 by writing directly to the device registers after power-up. The input block selects which of the two input ports is available for use by the synthesizer block. The output block provides two separate clock channels that are fully programmable. The synthesizer block multiplies and filters the input clock selected by the input block.

#### NOTE:

This Section of the data sheet provides a high-level description of the features of the CDCE62002 for purpose of understanding its capabilities. For a complete description of device registers and I/O, refer to the Device Configuration Section.

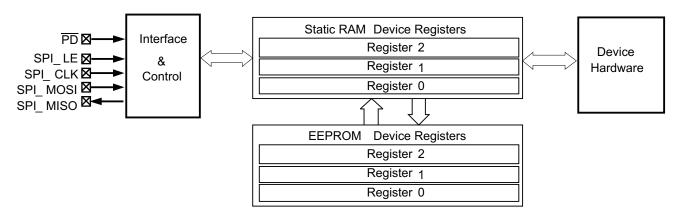

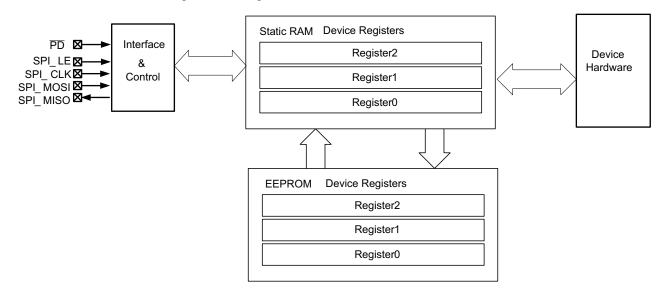

#### Interface and Control Block

The CDCE62002 is a highly flexible and configurable architecture and as such contains a number of registers so that the user may specify device operation. The contents of nine 28-bit wide registers implemented in static RAM determine device configuration at all times. On power-up, the CDCE62002 copies the contents of the EEPROM into the RAM and the device begins operation based on the default configuration stored in the EEPROM. Systems that do not have a host system to communicate with the CDCE62002 use this method for device configuration. The CDCE62002 provides the ability to lock the EEPROM; enabling the designer to implement a fault tolerant design. After power-up, the host system may overwrite the contents of the RAM via the SPI (Serial Peripheral Interface) port. This enables the configuration and reconfiguration of the CDCE62002 during system operation. Finally, the device offers the ability to copy the contents of the RAM into EEPROM, if the EEPROM is unlocked.

Figure 3. CDCE62002 Interface and Control Block

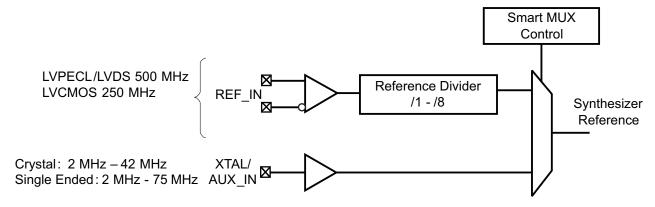

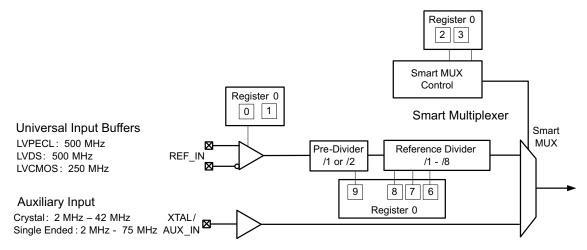

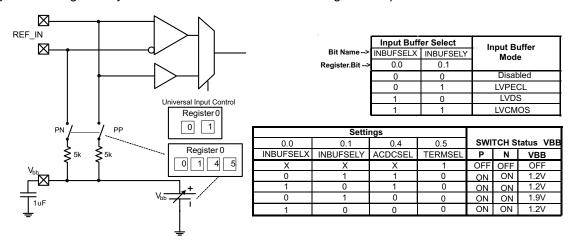

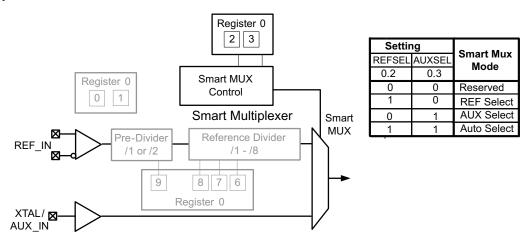

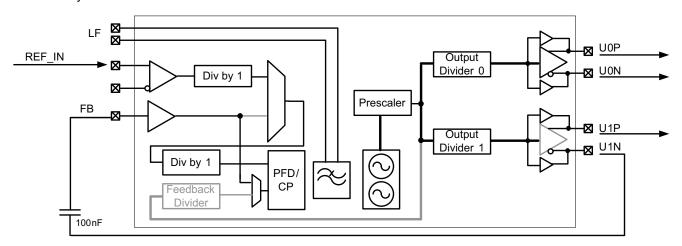

#### **Input Block**

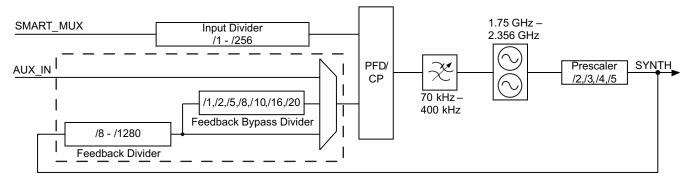

The Input Block includes one Universal Input Buffer and an Auxiliary Input. The Input Block buffers the incoming signals and facilitates signal routing to the Internal Synthesizer Block via the smart multiplexer (called the Smart MUX). The CDCE62002 can divide the REF\_IN signal via the dividers present on the inputs of the first stage of the Smart MUX.

Figure 4. CDCE62002 Input Block

Copyright © 2009, Texas Instruments Incorporated

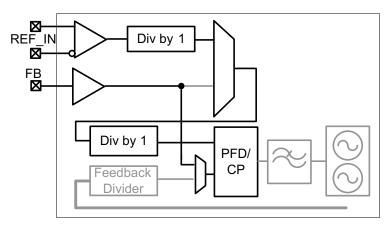

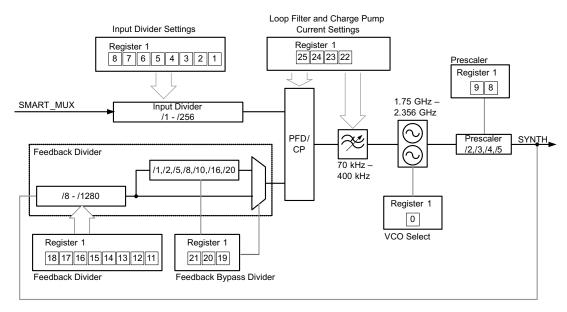

#### Synthesizer Block

Figure 5 presents a high-level overview of the Synthesizer Block on the CDCE62002. This block contains the Phase lock loop, internal loop filter and dual Voltage controlled oscillators. Only one VCO is selected at a time. The loop is closed after a Prescaler divider that feeds the output stage the feedback divider.

Figure 5. CDCE62002 Synthesizer Block

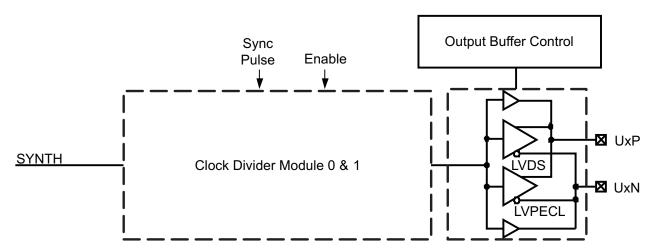

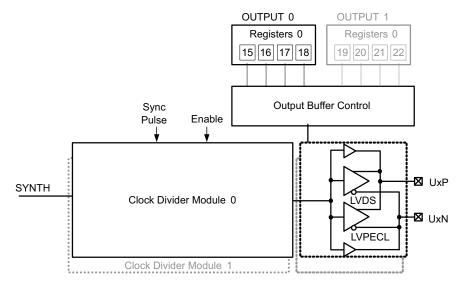

## **Output Block**

Both identical output blocks incorporate a Clock Divider Module (CDM), and a universal output array buffer driver. If an individual clock output channel is not used, then the user should disable the CDM and Output Buffer for the unused channel to save device power. Each channel includes 4-bit in register "0" to control the divide ratio. The output divider supports divide ratios from divide by 1 (bypass the divider) 2,3,4,5,8,10,12,16,20,24 and 32.

Figure 6. CDCE62002 Output Block

#### COMPUTING THE OUTPUT FREQUENCY

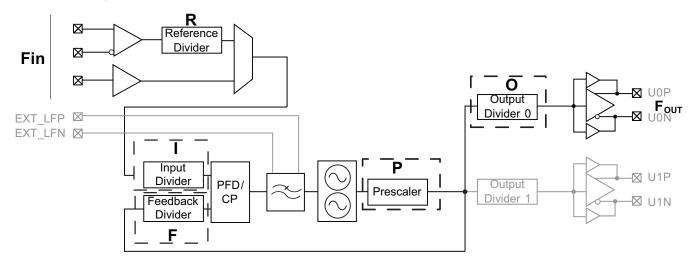

Figure 7 presents the block diagram of the CDCE62002 synthesizer highlighting the clock path for a single output. It also identifies the following regions containing dividers comprising the complete clock path:

- R: Is the Reference divider values.

- O: The output divider value (see Output Block for more details)

- I: The input divider value (see Synthesizer Block for more details)

- P: The Prescaler divider value (see Synthesizer Block of more details)

- F: The cumulative divider value of all dividers falling within the feedback divider (see Synthesizer Block for more details)

Figure 7. CDCE62002 Clock Path - Synthesizer

With respect to Figure 7, any output frequency generated by the CDCE62002 relates to the input frequency connected to the Synthesizer Block by the following equation:

$$F_{OUT} = F_{IN} \cdot \frac{F}{R \cdot I \cdot O} \tag{1}$$

Equation 1 holds true subject to the following constraints:

$$1.750GHz < O \cdot P \cdot F_{OUT} < 2.356GHz \tag{2}$$

And the comparison frequency  $F_{COMP}$ ,

$40.0 \text{ kHz} \le F_{COMP} \le 40 \text{ MHz}$

Where:

$$\mathsf{F}_{\mathsf{COMP}} = \frac{\mathsf{F}_{\mathsf{IN}}}{\mathsf{R} \cdot \mathsf{I}} \tag{3}$$

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                  | VALUE / UNIT          |

|----------------------------------------------------------------------------------|-----------------------|

| Supply voltage range VCC <sup>(2)</sup>                                          | -0.5 V to 4.6 V       |

| Input voltage range, V <sub>I</sub> <sup>(3)</sup>                               | -0.5 V to VCC + 0.5 V |

| Output voltage range, V <sub>O</sub> <sup>(3)</sup>                              | -0.5 V to VCC + 0.5 V |

| Input Current (V <sub>I</sub> < 0, V <sub>I</sub> > VCC)                         | ±20 mA                |

| Output current for LVPECL/LVCMOS Outputs (0 < V <sub>O</sub> < V <sub>CC</sub> ) | ±50 mA                |

| Maximum junction temperature, T <sub>J</sub>                                     | 125°C                 |

| Storage temperature range, T <sub>stg</sub>                                      | −65°C to 150°C        |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

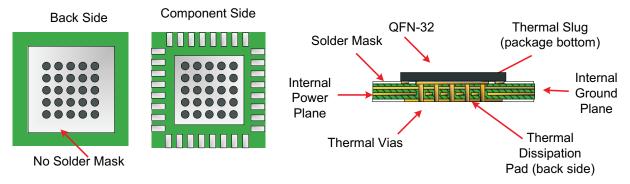

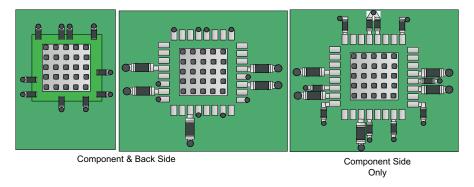

Package Thermal Resistance for QFN (RGZ) Package

| Airflow (Ifm) |                                         | θ <sub>JP</sub> (°C/W) | θJA (°C/W) |

|---------------|-----------------------------------------|------------------------|------------|

| 0             | JEDEC Compliant Board (3X3 VIAs on PAD) | 1.13                   | 35         |

| 200           | JEDEC Compliant Board (3X3 VIAs on PAD) | 1.13                   | 28.3       |

| 400           | JEDEC Compliant Board (3X3 VIAs on PAD) | 1.13                   | 27.2       |

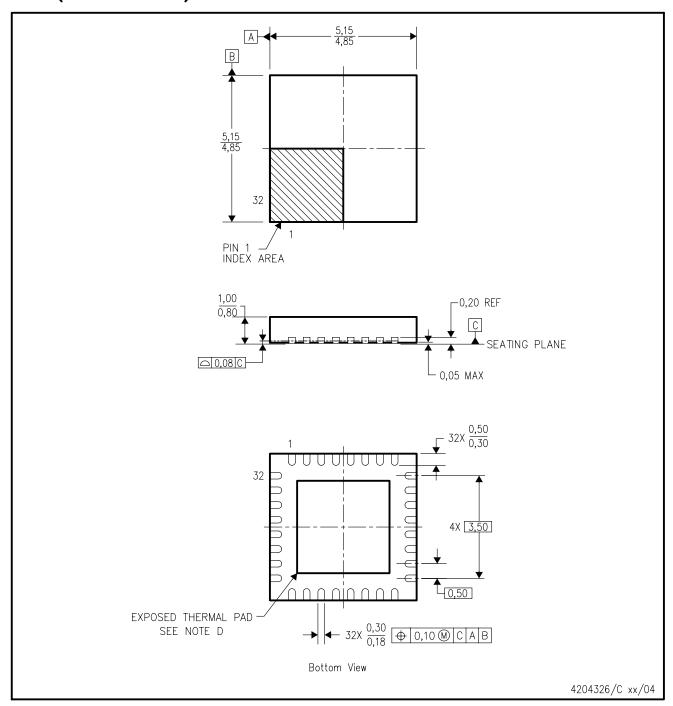

#### **PACKAGE**

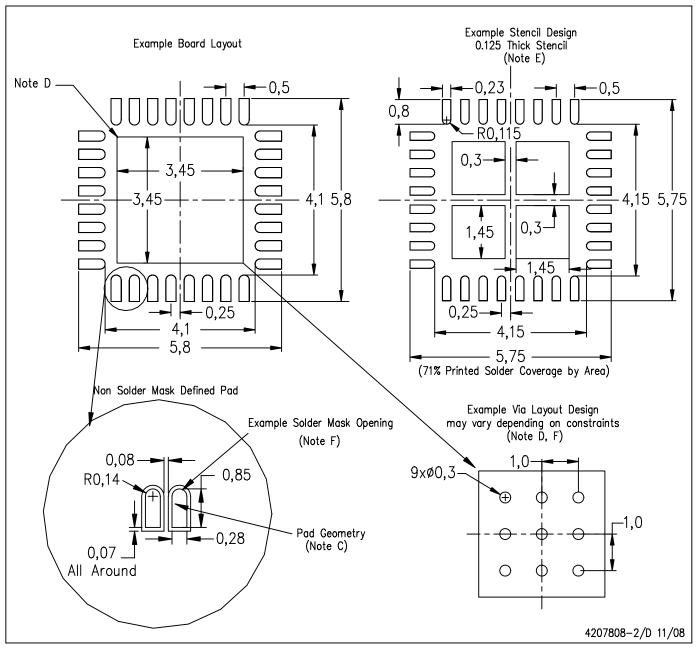

The CDCE62002 is packaged in a 32-Pin Lead Free "Green" Plastic Quad Flatpack Package with enhanced bottom thermal pad for heat dissipation. The Texas Instruments Package Designator is; RHB (S-PQFP-N32). Please refer to the Mechanical Data appendix at the end of this document for more information.

## **ELECTRICAL CHARACTERISTICS**

recommended operating conditions for the CDCE62002 Device for under the specified Industrial temperature range of -40°C to 85°C

|                     | PARAMETER TE                                                                                                 |                                             | ST CONDITIONS                                                                          | MIN | TYP <sup>(1)</sup> | MAX                 | UNIT |

|---------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|-----|--------------------|---------------------|------|

| POWER S             | SUPPLY                                                                                                       |                                             |                                                                                        |     |                    |                     |      |

| Supply vol          | Itage, $V_{CC\_OUT}$ , $V_{CC\_PLLDIV}$ , $V_{CC\_PLLD}$ , $V_{CC}$                                          | $_{\text{C_IN}}$ , and $V_{\text{CC\_AUX}}$ |                                                                                        | 3   | 3.3                | 3.6                 | V    |

| Analog Su           | Analog Supply Voltage, VCC_PLLA, & VCC_VCO                                                                   |                                             |                                                                                        |     | 3.3                | 3.6                 | V    |

| P <sub>LVPECL</sub> | REF at 30.72MHz<br>Outputs are LVPECL                                                                        | Output 1 = 491.5                            | 52 MHz                                                                                 |     | 850                |                     | mW   |

| P <sub>LVDS</sub>   | REF at 30.72MHz<br>Outputs are LVDS                                                                          | Output 2 = 245.7<br>In case of LVCM         | Output 1 = 491.32 Min2 Output 2 = 245.76 MHz In case of LVCMOS Outputs (1) = 245.76MHz |     | 750                |                     | mW   |

| P <sub>LVCMOS</sub> | REF at 30.72MHz<br>Outputs are LVCMOS                                                                        | 245.76MHz                                   |                                                                                        |     | 800                |                     | mW   |

| P <sub>OFF</sub>    | REF at 30.72MHz                                                                                              | Dividers and Outputs are disabled           |                                                                                        |     | 450                |                     | mW   |

| P <sub>PD</sub>     |                                                                                                              | Device is Power                             | ed Down                                                                                |     | 40                 |                     | mW   |

| DIFFEREN            | NTIAL INPUT MODE (REF_IN)                                                                                    | ·                                           |                                                                                        |     |                    |                     |      |

| Input ampl          | litude, VINPP (V <sub>IN+</sub> – V <sub>IN-</sub> )                                                         |                                             |                                                                                        | 0.1 |                    | 1.3                 | V    |

| Common-r            | mode input voltage, VIC                                                                                      |                                             |                                                                                        | 1.0 |                    | V <sub>CC</sub> -03 | V    |

| I <sub>IH</sub>     | Differential input current High (No in                                                                       | iternal Termination)                        | VI = VCC,<br>VCC = 3.6 V                                                               |     |                    | 20                  | μΑ   |

| I <sub>IL</sub>     | $I_{IL}$ Differential input current Low (No internal Termination) $VI = 0 \text{ V}, \\ VCC = 3.6 \text{ V}$ |                                             |                                                                                        |     |                    |                     | μΑ   |

| Input Capa          | acitance on REF_IN                                                                                           |                                             |                                                                                        |     | 3                  |                     | pF   |

| LVCMOS              | INPUT MODE (AUX_IN)                                                                                          |                                             |                                                                                        |     |                    | ,                   |      |

| V <sub>IL</sub>     | Low-level input voltage LVCMOS                                                                               |                                             |                                                                                        | 0   |                    | 0.3 VCC             | V    |

<sup>(1)</sup> All typical values are at VCC = 3.3 V, temperature = 25°C.

<sup>2)</sup> All supply voltages have to be supplied simultaneously.

<sup>(3)</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

## **ELECTRICAL CHARACTERISTICS (continued)**

recommended operating conditions for the CDCE62002 Device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

|                    | PARAMETER                                    | TES                         | T CONDITIONS              | MIN     | TYP <sup>(1)</sup> | MAX      | UNIT   |

|--------------------|----------------------------------------------|-----------------------------|---------------------------|---------|--------------------|----------|--------|

| V <sub>IH</sub>    | /IH High-level input voltage LVCMOS          |                             |                           | 0.7 VCC |                    | VCC      | V      |

| V <sub>IK</sub>    | LVCMOS input clamp voltage                   | VCC = 3 V, II = -           | -18 mA                    |         |                    | -1.2     | V      |

| I <sub>IH</sub>    | LVCMOS input current                         | VI = VCC, VCC :             | = 3.6 V                   |         | 300                |          | μΑ     |

| I <sub>IL</sub>    | LVCMOS input                                 | VI = 0 V, VCC =             | 3.6 V                     | -10     |                    | 10       | μΑ     |

| Cı                 | Input capacitance (LVCMOS signals)           | VI = 0 V or VCC             | 8                         |         | 8                  |          | pF     |

| CRYSTAL            | INPUT SPECIFICATIONS                         |                             |                           |         |                    |          |        |

|                    | Crystal Shunt Capacitance                    |                             |                           |         |                    | 10       | pF     |

|                    | Equivalent Series Resistance (ESR)           |                             |                           |         |                    | 50       | Ω      |

| LVCMOS             | INPUT MODE (SPI_CLK,SPI_MOSI,SPI_LE,         | PD, REF_IN)                 |                           |         |                    |          |        |

| V <sub>IL</sub>    | Low-level input voltage LVCMOS               |                             |                           | 0       |                    | 0.3 VCC  | V      |

| $V_{IH}$           | High-level input voltage LVCMOS              |                             |                           | 0.7 VCC |                    | VCC      | V      |

| $V_{IK}$           | LVCMOS input clamp voltage                   | VCC = 3 V, II = -           | -18 mA                    |         |                    | -1.2     | V      |

| I <sub>IH</sub>    | LVCMOS input current VI =                    | VCC, VCC = 3.6              | V                         |         |                    | 20       | μΑ     |

| I <sub>IL</sub>    | LVCMOS input (Except REF_IN)                 | VI = 0 V, VCC =             | 3.6 V                     | -10     |                    | -40      | μΑ     |

| I <sub>IL</sub>    | LVCMOS input (REF_IN)                        | VI = 0 V, VCC =             | VI = 0 V, VCC = 3.6 V     |         |                    | 10       | μΑ     |

| Cı                 | Input capacitance (LVCMOS signals)           | VI = 0 V or VCC             | 3                         |         | 3                  |          | pF     |

| SPI OUTP           | UT (MISO) / PLL                              |                             |                           |         |                    |          |        |

| I <sub>OH</sub>    | High-level output current                    | VCC = 3.3 V,                | V <sub>O</sub> = 1.65 V   |         | -30                |          | mA     |

| I <sub>OL</sub>    | Low-level output current                     | VCC = 3.3 V,                | V <sub>O</sub> = 1.65 V   |         | 33                 |          | mA     |

| V <sub>OH</sub>    | High-level output voltage for LVCMOS outputs | VCC = 3 V,                  | I <sub>OH</sub> = -100 μA | VCC-0.5 |                    |          | V      |

| V <sub>OL</sub>    | Low-level output voltage for LVCMOS outputs  | VCC = 3 V,                  | Ι <sub>ΟΗ</sub> = 100 μΑ  |         |                    | 0.3      | V      |

| Co                 | Output capacitance o MISO                    | VCC = 3.3 V; V <sub>O</sub> | = 0 V or VCC              |         | 3                  |          | pF     |

| I <sub>OZH</sub>   |                                              | ., ., .,                    | <b></b>                   |         | 5                  |          | μΑ     |

| I <sub>OZL</sub>   | 3-state output current                       | $V_O = V_{CC}, V_O = 0$     | ) V                       |         | -5                 |          | μΑ     |

| EEPROM             | ,                                            |                             |                           | •       |                    | '        |        |

| EEcyc              | Programming cycle of EEPROM                  |                             |                           | 100     | 1000               |          | Cycles |

| EEret              | Data retention                               |                             |                           | 10      |                    |          | Years  |

| VBB ( INP          | UT BUFFER INTERNAL TERMINATION VO            | LTAGE REFERENC              | CE)                       | •       |                    | <u>'</u> |        |

| $V_{BB}$           | Input termination voltage                    | IBB = -0.2 mA, [            | Depending on the setting  | 1.2     |                    | 1.9      | V      |

| INPUT BU           | FFERS INTERNAL TERMINATION RESIST            | ORS (REF_IN)                |                           | •       |                    | <u>'</u> |        |

|                    | Termination resistance                       | Single ended                |                           |         | 5                  |          | kΩ     |

| PHASE DI           | ETECTOR                                      | *                           |                           | •       |                    |          |        |

| f <sub>CPmax</sub> | Charge pump frequency                        |                             |                           | 0.04    |                    | 40       | MHz    |

## **ELECTRICAL CHARACTERISTICS (Continued)**

recommended operating conditions for the CDCE62002 Device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

|                        | PARAMETER                                    |                                         | NDITIONS                   | MIN     | TYP <sup>(1)</sup> | MAX | UNIT |

|------------------------|----------------------------------------------|-----------------------------------------|----------------------------|---------|--------------------|-----|------|

| LVCMOS                 |                                              |                                         |                            | "       |                    |     |      |

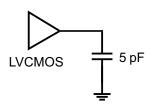

| f <sub>clk</sub>       | Output frequency, see Figure below           | Load = 5 pF to GN                       | D                          |         |                    | 250 | MHz  |

| V <sub>OH</sub>        | High-level output voltage for LVCMOS outputs | V <sub>CC</sub> = min to max            | $I_{OH} = -100 \mu A$      | VCC-0.5 |                    |     | V    |

| V <sub>OL</sub>        | Low-level output voltage for LVCMOS outputs  | V <sub>CC</sub> = min to max            | $I_{OL} = 100 \mu\text{A}$ |         |                    | 0.3 | V    |

| I <sub>OH</sub>        | High-level output current                    | VCC = 3.3 V                             | VO = 1.65 V                |         | -30                |     | mA   |

| I <sub>OL</sub>        | Low-level output current                     | VCC = 3.3 V                             | VO = 1.65 V                |         | 33                 |     | mA   |

| t <sub>sko</sub>       | Skew, output to output For Y0 to Y1          | Both Outputs set a<br>Reference = 30.72 |                            |         | 75                 |     | ps   |

| Co                     | Output capacitance on Y0 to Y1               | VCC = 3.3 V; VO =                       | = 0 V or VCC               |         | 5                  |     | pF   |

| I <sub>OZH</sub>       | Tristate LVCMOS output current               | VO = VCC                                |                            |         | 5                  |     | μΑ   |

| I <sub>OZL</sub>       | Tristate LVCMOS output current               | VO = 0 V                                |                            |         | -5                 |     | μΑ   |

| I <sub>OPDH</sub>      | Power Down output current                    | VO = VCC                                |                            |         |                    | 25  | μΑ   |

| I <sub>OPDL</sub>      | Power Down output current                    | VO = 0 V                                |                            |         |                    | 5   | μΑ   |

| Duty cycle             | LVCMOS                                       |                                         |                            | 45%     |                    | 55% |      |

| t <sub>slew-rate</sub> | Output rise/fall slew rate                   |                                         |                            | 3.6     | 5.2                |     | V/ns |

(1) All typical values are at VCC = 3.3 V, temperature = 25°C.

## **ELECTRICAL CHARACTERISTICS (Continued)**

recommended operating conditions for the CDCE62002 Device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

|                                 | PARAMETER                                   | TEST CONDITIONS                                         | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------------------|---------------------------------------------|---------------------------------------------------------|-----|--------------------|-----|------|

| LVDS C                          | DUTPUT                                      |                                                         |     |                    |     |      |

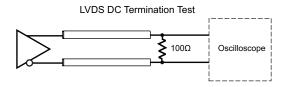

| f <sub>clk</sub>                | Output frequency                            | Configuration Load (see Figure below)                   | 0   |                    | 800 | MHz  |

| VOD                             | Differential output voltage                 | R <sub>L</sub> = 100 Ω                                  | 270 |                    | 550 | mV   |

| $\Delta V_{OD}$                 | LVDS VOD Magnitude Change                   |                                                         |     |                    | 50  | mV   |

| Vos                             | Offset Voltage                              | -40°C to 85°C                                           |     | 1.24               |     | V    |

| $\Delta V_{OS}$                 | VOS Magnitude Change                        |                                                         |     | 40                 |     | mV   |

|                                 | Short Circuit Vout+ to Ground               | VOUT = 0                                                |     |                    | 27  | mA   |

|                                 | Short Circuit Vout- to Ground               | VOUT = 0                                                |     |                    | 27  | mA   |

| t <sub>sk(o)</sub>              | Skew, output to output For Y0 to Y1         | Both Outputs set at 122.88 MHz<br>Reference = 30.72 MHz |     | 10                 |     | ps   |

| Co                              | Output capacitance on Y0 to Y1              | VCC = 3.3 V; VO = 0 V or VCC                            |     | 5                  |     | pF   |

| I <sub>OPDH</sub>               | Power Down output current                   | VO= V <sub>CC</sub>                                     |     |                    | 25  | μΑ   |

| I <sub>OPDL</sub>               | Power Down output current                   | VO= 0 V                                                 |     |                    | 5   | μΑ   |

|                                 | Duty Cycle                                  |                                                         | 45% |                    | 55% |      |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time                          | 20% to 80% of Voutpp                                    | 110 | 160                | 190 | ps   |

| LVCMO                           | S-TO-LVDS                                   |                                                         |     |                    |     |      |

| t <sub>skP C</sub>              | Output skew between LVCMOS and LVDS outputs | VCC/2 to Crosspoint                                     | 1.4 | 1.7                | 2.0 | ns   |

<sup>(1)</sup> All typical values are at VCC = 3.3 V, temperature = 25°C.

## **ELECTRICAL CHARACTERISTICS (Continued)**

recommended operating conditions for the CDCE62002 Device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

| PARAMET                         | ER                                            | TEST CONDITIONS                       | MIN       | TYP <sup>(1)</sup> | MAX       | UNIT |

|---------------------------------|-----------------------------------------------|---------------------------------------|-----------|--------------------|-----------|------|

| LVPECL O                        | UTPUT                                         |                                       |           |                    |           |      |

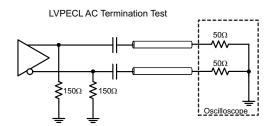

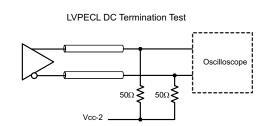

| f <sub>clk</sub>                | Output frequency,                             | Configuration Load (see Figure below) | 0         |                    | 1175      | MHz  |

| $V_{OH}$                        | LVPECL high-level output voltage              | Load                                  | VCC -1.1  |                    | VCC -0.88 | V    |

| $V_{OL}$                        | LVPECL low-level output voltage               | Load                                  | VCC -2.02 |                    | VCC -1.48 | V    |

| VOD                             | Differential output voltage                   |                                       | 510       |                    | 870       | mV   |

| t <sub>sko</sub>                | Skew, output to output For Y0 to Y1           | Both Outputs set at 122.88 MHz        |           | 15                 |           | ps   |

| со                              | Output capacitance on Y0 to Y1                | VCC = 3.3 V; VO = 0 V or VCC          |           | 5                  |           | pF   |

| I <sub>OPDH</sub>               | Power Down output current                     | VO= V <sub>CC</sub>                   |           |                    | 25        | μΑ   |

| I <sub>OPDL</sub>               | Power Down output current                     | VO= 0 V                               |           |                    | 5         | μΑ   |

|                                 | Duty Cycle                                    |                                       | 45%       |                    | 55%       |      |

| $t_r / t_f$                     | Rise and fall time                            | 20% to 80% of Voutpp                  | 55        | 75                 | 735       | ps   |

| LVDS-TO-                        | LVPECL                                        |                                       |           |                    |           |      |

| t <sub>skP_C</sub>              | Output skew between LVDS and LVPECL outputs   | Crosspoint to Crosspoint              | 130       | 200                | 280       | ps   |

| LVCMOS-                         | TO- LVPECL                                    |                                       |           |                    |           |      |

| t <sub>skP_C</sub>              | Output skew between LVCMOS and LVPECL outputs | VCC/2 to Crosspoint                   | 1.6       | 1.8                | 2.2       | ns   |

| LVPECL H                        | i-PERFORMANCE OUTPUT                          |                                       |           |                    |           |      |

| V <sub>OH</sub>                 | LVPECL high-level output voltage              | Load                                  | VCC -1.11 |                    | VCC -0.91 | V    |

| V <sub>OL</sub>                 | LVPECL low-level output voltage               | Load                                  | VCC -2.06 |                    | VCC -1.84 | V    |

| VOD                             | Differential output voltage                   |                                       | 670       |                    | 950       | mV   |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time                            | 20% to 80% of Voutpp                  | 55        | 75                 | 135       | ps   |

<sup>(1)</sup> All typical values are at VCC = 3.3 V, temperature = 25°C.

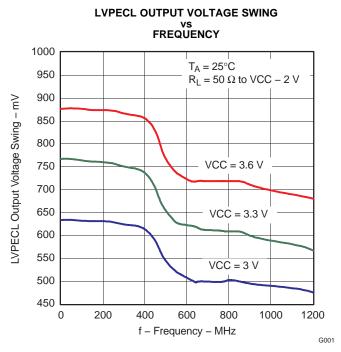

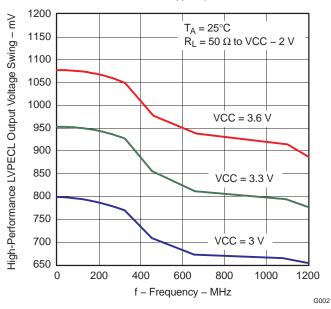

# HIGH-PERFORMANCE LVPECL OUTPUT VOLTAGE SWING vs FREQUENCY $T_A = 25^{\circ}C$

Figure 8.

Figure 9. LVCMOS OUTPUT VOLTAGE SWING

vs FREQUENCY 3.8  $T_A = 25^{\circ}C$ 3.7  $C_L = 5 pF$ VCC = 3.6 V 3.6 LVCMOS Output Voltage Swing - V 3.5 3.4 VCC = 3.3 V3.3 3.2 3.1 VCC = 3 V3.0 2.9 2.8 2.7

50

100

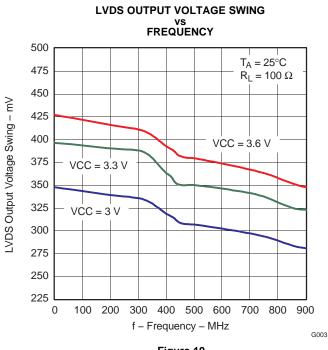

Figure 10.

f - Frequency - MHz Figure 11.

200

150

300

G004

## **TIMING REQUIREMENTS**

over recommended ranges of supply voltage, load and operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                                                                    | MIN | TYP | MAX | UNIT |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| REF_IN REQUIREM                 | REF_IN REQUIREMENTS                                                                                          |     |     |     |      |  |  |  |

| f <sub>REF - Diff IN-DIV</sub>  | Maximum clock frequency applied to reference divider when (Register 0 Bit $9 = 1$ ) (Reg 0 RAM bit $9 = 1$ ) |     |     | 500 | MHz  |  |  |  |

| f <sub>REF - Diff REF_DIV</sub> | Maximum clock frequency applied to reference divider when (Register 0 Bit $9=0$ ) (Reg 0 RAM bit $9=0$ )     |     |     | 250 | MHz  |  |  |  |

| f <sub>REF- Single</sub>        | For Single ended Inputs ( LVCMOS) on REF_IN                                                                  |     |     | 250 | MHz  |  |  |  |

| Duty Cycle Single               | Duty cycle of REF_IN at V <sub>CC</sub> / 2                                                                  | 40% |     | 60% |      |  |  |  |

| Duty Cycle Diff                 | Duty cycle of REF_IN at V <sub>CC</sub> / 2                                                                  | 40% |     | 60% |      |  |  |  |

| AUXILARY_IN REQ                 | UIREMENTS                                                                                                    |     |     |     |      |  |  |  |

| f <sub>REF - Single</sub>       | For Single ended Inputs (LVCMOS) on AUX_IN                                                                   | 2   |     | 75  | MHz  |  |  |  |

| f <sub>REF - Crystal</sub>      | For Single ended Inputs (AT-Cut Crystal Input)                                                               | 2   |     | 42  | MHz  |  |  |  |

| PD REQUIREMENT                  | S                                                                                                            |     |     |     |      |  |  |  |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time of the PD signal from 20% to 80% of V <sub>CC</sub>                                       |     |     | 4   | ns   |  |  |  |

## **PHASE NOISE ANALYSIS**

## Table 2. Phase Noise for 30.72MHz External Reference

| PHASE NOISE              | Reference          | LVPECL-HP | LVPECL    | LVDS-HP   | LVDS      | LVCMOS-HP | LVCMOS    | UNIT   |

|--------------------------|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|--------|

| AT                       | 30.72MHz           | 491.52MHz | 491.52MHz | 491.52MHz | 491.52MHz | 122.88MHz | 122.88MHz |        |

| 10Hz                     | -108               | -84       | -84       | -85       | -85       | -97       | -97       | dBc/Hz |

| 100Hz                    | -130               | -98       | -98       | -98       | -97       | -110      | -111      | dBc/Hz |

| 1kHz                     | -134               | -106      | -106      | -106      | -106      | -118      | -118      | dBc/Hz |

| 10kHz                    | -152               | -118      | -118      | -118      | -118      | -130      | -130      | dBc/Hz |

| 100kHz                   | -156               | -121      | -121      | -121      | -121      | -133      | -133      | dBc/Hz |

| 1MHz                     | -157               | -131      | -131      | -130      | -130      | -143      | -142      | dBc/Hz |

| 10MHz                    | _                  | -146      | -146      | -146      | -145      | -152      | -151      | dBc/Hz |

| 20MHz                    | _                  | -146      | -146      | -146      | -145      | -152      | -151      | dBc/Hz |

| Jitter(RMS)<br>10k~20MHz | 195<br>(10k~20Mhz) | 319       | 316       | 332.4     | 332.2     | 366.5     | 372.1     | fs     |

## Table 3. Phase Noise for 25MHz Crystal Reference

| Phase Noise Specifications under following configuration: VCO = 2000.00 MHz, AUX_IN -REF = 25.00MHz, PFD Frequency = 25.00MHz, Charge Pump Current = 1.5mA Loop BW = 400kHz 3.3V and 25°C. |                       |                        |                      |                        |        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|----------------------|------------------------|--------|--|--|--|--|

| Phase Noise at                                                                                                                                                                             | Reference<br>25.00MHz | LVPECL-HP<br>500.00MHz | LVDS-HP<br>250.00MHz | LVCMOS-HP<br>125.00MHz | UNIT   |  |  |  |  |

| 10Hz                                                                                                                                                                                       | _                     | -72                    | -72                  | -79                    | dBc/Hz |  |  |  |  |

| 100Hz                                                                                                                                                                                      | _                     | -97                    | -97                  | -103                   | dBc/Hz |  |  |  |  |

| 1kHz                                                                                                                                                                                       | _                     | -111                   | -111                 | -118                   | dBc/Hz |  |  |  |  |

| 10kHz                                                                                                                                                                                      | _                     | -120                   | -120                 | -126                   | dBc/Hz |  |  |  |  |

| 100kHz                                                                                                                                                                                     | _                     | -124                   | -124                 | -130                   | dBc/Hz |  |  |  |  |

| 1MHz                                                                                                                                                                                       | _                     | -136                   | -136                 | -142                   | dBc/Hz |  |  |  |  |

| 10MHz                                                                                                                                                                                      | _                     | -147                   | -147                 | -151                   | dBc/Hz |  |  |  |  |

| 20MHz                                                                                                                                                                                      | _                     | -148                   | -148                 | -151                   | dBc/Hz |  |  |  |  |

| Jitter(RMS)<br>10k~20MHz                                                                                                                                                                   | _                     | 426                    | 426                  | 443                    | fs     |  |  |  |  |

#### **OUTPUT TO OUTPUT ISOLATION**

## **Measurement Method**

- 1. Connect output 1 to the phase noise and Spectrum analyzer.

- 2. Measure spurious on Outputs 1.

- 3. Enable aggressor channel 0

- 4. Measure spurious on Output 1

- 5. The difference between the spurious levels of Outputs 1 before and after enabling the aggressor channel determine the output-to-output isolation performance recorded.

## **Table 4. Output to Output Isolation**

|                   |                                  |                                  | WORST CASE SPUR              | UNIT |

|-------------------|----------------------------------|----------------------------------|------------------------------|------|

| The Output to Out | put Isolation was tested at 3.3V | supply and 25°C ambient temperat | ure (Default Configuration): |      |

| Output 1          | Measured Channel                 | In LVDS Signaling at 125MHz      | -70                          | dB   |

| Output 0          | Aggressor Channel                | LVPECL 156.25MHz                 |                              |      |

Copyright © 2009, Texas Instruments Incorporated

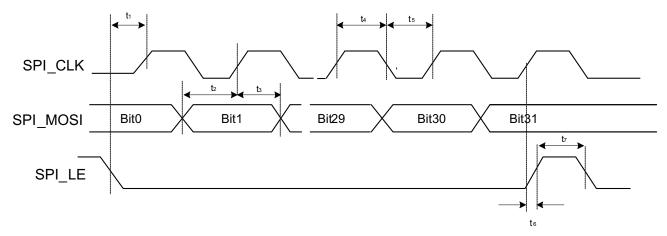

## SPI CONTROL INTERFACE TIMING

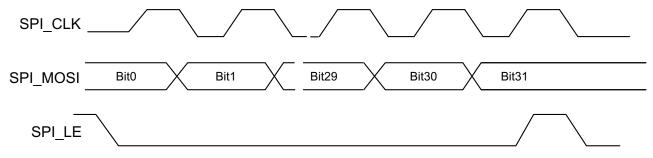

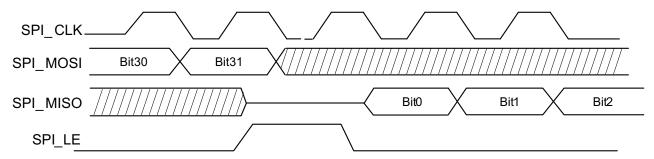

Figure 12. Timing Diagram for SPI Write Command

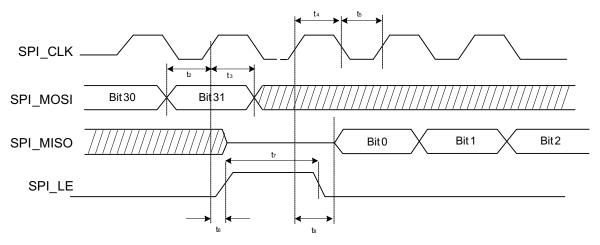

Figure 13. Timing Diagram for SPI Read Command

**Table 5. SPI Bus Timing Characteristics**

|                    | SPI BUS TIMINGS                                           |     |     |     |      |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|--|--|

|                    | PARAMETER                                                 | MIN | TYP | MAX | UNIT |  |  |  |  |  |  |  |

| f <sub>Clock</sub> | Clock Frequency for the SPI_CLK                           |     |     | 20  | MHz  |  |  |  |  |  |  |  |

| t <sub>1</sub>     | SPI_LE to SPI_CLK setup time                              | 10  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>2</sub>     | SPI_MOSI to SPI_CLK setup time                            | 10  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>3</sub>     | SPI_MOSI to SPI_CLK hold time                             | 10  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>4</sub>     | SPI_CLK high duration                                     | 25  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>5</sub>     | SPI_CLK low duration                                      | 25  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>6</sub>     | SPI_CLK to SPI_LE Setup time                              | 10  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>7</sub>     | SPI_LE Pulse Width                                        | 20  |     |     | ns   |  |  |  |  |  |  |  |

| t <sub>8</sub>     | SPI_MISO to SPI_CLK Data Valid (First Valid Bit after LE) | 10  |     |     | ns   |  |  |  |  |  |  |  |

## **DEVICE CONFIGURATION**

The Functional Description Section described four different functional blocks contained within the CDCE62002. Figure 14 depicts these blocks along with a high-level functional block diagram of the circuit elements comprising each block. The balance of this section focuses on a detailed discussion of each functional block from the perspective of how to configure them.

Figure 14. CDCE62002 Circuit Blocks

## **INTERFACE and CONTROL BLOCK**

The Interface and Control Block includes a SPI interface, four control pins, a non-volatile memory array in which the device stores default configuration data, and an array of device registers implemented in Static RAM. This RAM, also called the device registers, configures all hardware within the CDCE62002.

Figure 15. CDCE62002 Interface and Control Block

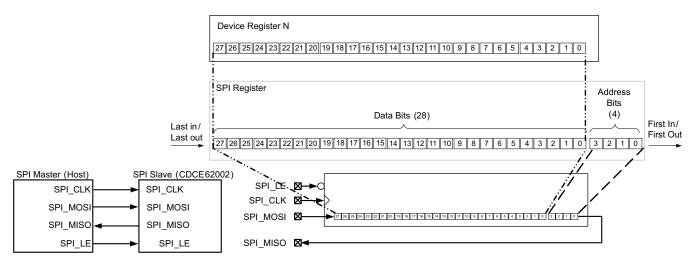

## **SPI (Serial Peripheral Interface)**

The serial interface of CDCE62002 is a simple bidirectional SPI interface for writing and reading to and from the device registers. It implements a low speed serial communications link in a master/slave topology in which the CDCE62002 is a slave. The SPI consists of four signals:

- SPI\_CLK: Serial Clock (Output from Master) the CDCE62002 clocks data in and out on the rising edge of SPI\_CLK. Data transitions therefore occur on the falling edge of the clock.

- SPI\_MOSI: Master Output Slave Input (Output from Master).

- SPI\_MISO: Master Input Slave Output (Output from Slave)

- SPI\_LE: Latch Enable (Output from Master). The falling edge of SPI\_LE initiates a transfer. If SPI\_LE is high, no data transfer can take place.

The CDCE62002 implements data fields that are 28-bits wide. In addition, it contains 3 registers, each comprising a 28 bit data field. Therefore, accessing the CDCE62002 requires that the host program append a 4-bit address field to the front of the data field as follows:

Figure 16. CDCE62002 SPI Communications Format

#### **CDCE62002 SPI Command Structure**

The CDCE62002 supports four commands issued by the Master via the SPI:

- Write to RAM

- Read Command

- Copy RAM to EEPROM unlock

- Copy RAM to EEPROM lock

Table 6 provides a summary of the CDCE62002 SPI command structure. The host (master) constructs a Write to RAM command by specifying the appropriate register address in the address field and appends this value to the beginning of the data field. Therefore, a valid command stream must include 32 bits, transmitted LSB first. The host must issue a Read Command to initiate a data transfer from the CDCE62002 back to the host. This command specifies the address of the register of interest in the data field.

Table 6. CDCE62002 SPI Command Structure

|             | Data Field (28 Bits) |          |        |        |        |        |   |     |        |        |        | Addr Field<br>(4 Blts) |        |        |   |   |   |   |   |        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-------------|----------------------|----------|--------|--------|--------|--------|---|-----|--------|--------|--------|------------------------|--------|--------|---|---|---|---|---|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Register    | Operation            | NVM      | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2 | 2 2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8                 | 1<br>7 | 1<br>6 |   | 1 | 1 | 1 |   | 1<br>0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 3 | 2 | 1 | 0 |

| 0           | Write to RAM         | Yes      | Х      | Х      | Х      | Х      | Х | Х   | Х      | Х      | Х      | Х                      | Х      | Х      | Х | Х | Χ | Х | Х | Х      | Х | Х | Х | Χ | Χ | Х | Х | Х | Х | Χ | 0 | 0 | 0 | 0 |

| 1           | Write to RAM         | Yes      | Х      | Х      | Х      | Х      | Х | Х   | Х      | Х      | Х      | Х                      | Х      | Х      | Х | Х | Χ | Х | Х | Х      | Х | Х | Х | Χ | Χ | Х | Х | Х | Х | Χ | 0 | 0 | 0 | 1 |

| 2           | Status/Control       | No       | Х      | Х      | Х      | Х      | Х | Х   | Х      | Х      | Х      | Х                      | Х      | Х      | Х | Х | Χ | Х | Х | Х      | Х | Х | Х | Χ | Χ | Х | Х | Х | Х | Χ | 0 | 0 | 1 | 0 |

| Instruction | Read Command         | No       | 0      | 0      | 0      | 0      | 0 | 0   | 0      | 0      | 0      | 0                      | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Α | Α | Α | Α | 1 | 1 | 1 | 0 |

| Instruction | RAM EEPROM           | Unlock   | 0      | 0      | 0      | 0      | 0 | 0   | 0      | 0      | 0      | 0                      | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| Instruction | RAM EEPROM           | Lock (1) | 0      | 0      | 0      | 0      | 0 | 0   | 0      | 0      | 0      | 0                      | 0      | 0      | 0 | 0 | 0 | 0 | 1 | 0      | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

(1) **CAUTION:** After execution of this command, the EEPROM is **permanently** locked. After locking the EEPROM, device configuration can only be changed via Write to RAM after power-up; however, the EEPROM can no longer be changed.

## Writing to the CDCE62002

Figure 17 illustrates a Write to RAM operation. Notice that the latching of the first data bit in the data stream (Bit 0) occurs on the first rising edge of SPI\_CLK after SPI\_LE transitions from a high to a low. For the CDCE62002, data transitions occur on the falling edge of SPI\_CLK. A rising edge on SPI\_LE signals to the CDCE62002 that the transmission of the last bit in the stream (Bit 31) has occurred.

Figure 17. CDCE62002 SPI Write Operation

## Reading from the CDCE62002

Figure 18 shows how the CDCE62002 executes a Read Command. The SPI master first issues a Read Command to initiate a data transfer from the CDCE62002 back to the host (see Table 6). This command specifies the address of the register of interest. By transitioning SPI\_LE from a low to a high, the CDCE62002 resolves the address specified in the appropriate bits of the data field. The host drives SPI\_LE low and the CDCE62002 presents the data present in the register specified in the Read Command on SPI\_MISO.

Figure 18. CDCE62002 Read Operation

## Writing to EEPROM

After the CDCE62002 detects a power-up and completes a reset cycle, it copies the contents of the on-board EEPROM into the Device Registers. Therefore, the CDCE62002 initializes into a known state predefined by the user. The host issues one of two special commands shown in Table 6 to copy the contents of Device Registers 0 through 1 into EERPOM. They include:

- Copy RAM to EEPROM Unlock, Execution of this command can happen many times.

- Copy RAM to EEPROM Lock: Execution of this command can happen only once; after which the EEPROM is permanently locked.

After either command is initiated, power must remain stable and the host must not access the CDCE62002 for at least 50 ms to allow the EEPROM to complete the write cycle and to avoid the possibility of EEPROM corruption.

Copyright © 2009, Texas Instruments Incorporated

# **Device Registers: Register 0**

# Table 7. CDCE62002 Register 0 Bit Definitions

| SPI<br>BIT | RAM<br>BIT | BIT<br>NAME  | RELATED<br>BLOCK | DESCRIPTION / FUNCTION                                                                                                                                                                                                                             |        |

|------------|------------|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 0          |            | A0           |                  | Address 0                                                                                                                                                                                                                                          | 0      |

| 1          |            | A1           |                  | Address 1                                                                                                                                                                                                                                          | 0      |

| 2          |            | A2           |                  | Address 2                                                                                                                                                                                                                                          | 0      |

| 3          |            | A3           |                  | Address 3                                                                                                                                                                                                                                          | 0      |

| 4          | 0          | INBUFSELX    | INBUFSELX        | Input Buffer Select (LVPECL,LVDS or LVCMOS)                                                                                                                                                                                                        | EEPROM |

| 5          | 1          | INBUFSELY    | INBUFSELY        | XY(00 ) Disabled, (01) LVPECL, (10) LVDS, (11) LVCMOS The VBB internal Biasing will be determined from this setting                                                                                                                                | EEPROM |

| 6          | 2          | REFSEL       | Smart MUX        | See specific section for more detailed description and configuration                                                                                                                                                                               | EEPROM |

| 7          | 3          | AUXSEL       | Bits(2,3)        | setup.  00 – RESERVED  10 – REF_IN Select  01– AUX_IN Select  11 – Auto Select ( Reference then AUX)                                                                                                                                               | EEPROM |

| 8          | 4          | ACDCSEL      | Input Buffers    | If Set to "1" DC Termination, If set to "0" AC Termination                                                                                                                                                                                         | EEPROM |

| 9          | 5          | TERMSEL      | Input Buffers    | If Set to "0" Input Buffer Internal Termination Enabled                                                                                                                                                                                            | EEPROM |

| 10         | 6          | REFDIVIDE 0  |                  |                                                                                                                                                                                                                                                    | EEPROM |

| 11         | 7          | REFDIVIDE 1  |                  | Reference Divider Settings. See specific section for more detailed description and configuration                                                                                                                                                   | EEPROM |

| 12         | 8          | REFDIVIDE 2  |                  | setup.                                                                                                                                                                                                                                             | EEPROM |

| 13         | 9          | REFDIVIDE 3  |                  |                                                                                                                                                                                                                                                    | EEPROM |

| 14         | 10         | EXTFEEDBACK  |                  | External Feedback to PFD from AUX Input enabled when set to "1"                                                                                                                                                                                    | EEPROM |

| 15         | 11         | I70TEST      | TEST             | Set to "0" for Normal Operation.                                                                                                                                                                                                                   | EEPROM |

| 16         | 12         | ATETEST      | TEST             | Set to "0" for Normal Operation.                                                                                                                                                                                                                   | EEPROM |

| 17         | 13         | LOCKW(0)     | PLL Lock         | Lock-detect window Bit 0                                                                                                                                                                                                                           | EEPROM |

| 18         | 14         | LOCKW(1)     | PLL Lock         | Lock-detect window Bit 1                                                                                                                                                                                                                           | EEPROM |