### INTEGRATED CIRCUITS

Product data sheet Supersedes data of 2004 Oct 05 2004 Dec 21

**SE95**

#### **GENERAL DESCRIPTION**

The SE95 is a temperature-to-digital converter using an on-chip band-gap temperature sensor and Sigma-delta A-to-D conversion technique. The device is also a thermal detector providing an over-temp detection output. The SE95 contains a number of data registers: Configuration register (Conf) to store the device settings such as sampling rate, device operation mode, OS operation mode, OS polarity, and OS fault queue as described in the functional description section; temperature register (Temp) to store the digital temp reading, and set-point registers (Tos & Thyst) to store programmable overtemp shutdown and hysteresis limits, and also an ID register to store manufacturer numbers. These registers are accessed by a controller via the 2-wire serial I<sup>2</sup>C-bus interface. The device includes an open-drain output (OS) which becomes active when the temperature exceeds the programmed limits. There are three selectable logic address pins so that eight devices can be connected on the same bus without address conflict.

The SE95 can be configured for different operation conditions. It can be set in normal mode to periodically monitor the ambient temperature, or in shutdown mode to minimize power consumption. The OS output operates in either of two selectable modes: OS comparator mode and OS interrupt mode. Its active state can be selected as either HIGH or LOW. The fault queue that defines the number of consecutive faults in order to activate the OS output is programmable as well as the set-point limits.

The temperature register always stores a 13-bit 2's complement data giving a temperature resolution of 0.03125 °C. This high temperature resolution is particularly useful in applications of measuring precisely the thermal drift or runaway. For normal operation and compatibility with the LM75A, only the 11 MSBs are read, with a resolution of 0.125 °C to provide the accuracies specified. To be compatible with the LM75, read only the 9 MSBs.

The device is powered-up in normal operation mode with the OS in comparator mode, temperature threshold of 80 °C and hysteresis of 75 °C, so that it can be used as a stand-alone thermostat with those pre-defined temperature set points. The conversion rate is programmable, with a default of 10 conversions/sec.

#### FEATURES

- Pin-for-pin replacement for industry standard LM75/LM75A and offers improved temperature resolution

- Specification of a single part over power supply range from 2.8 V to 5.5 V.

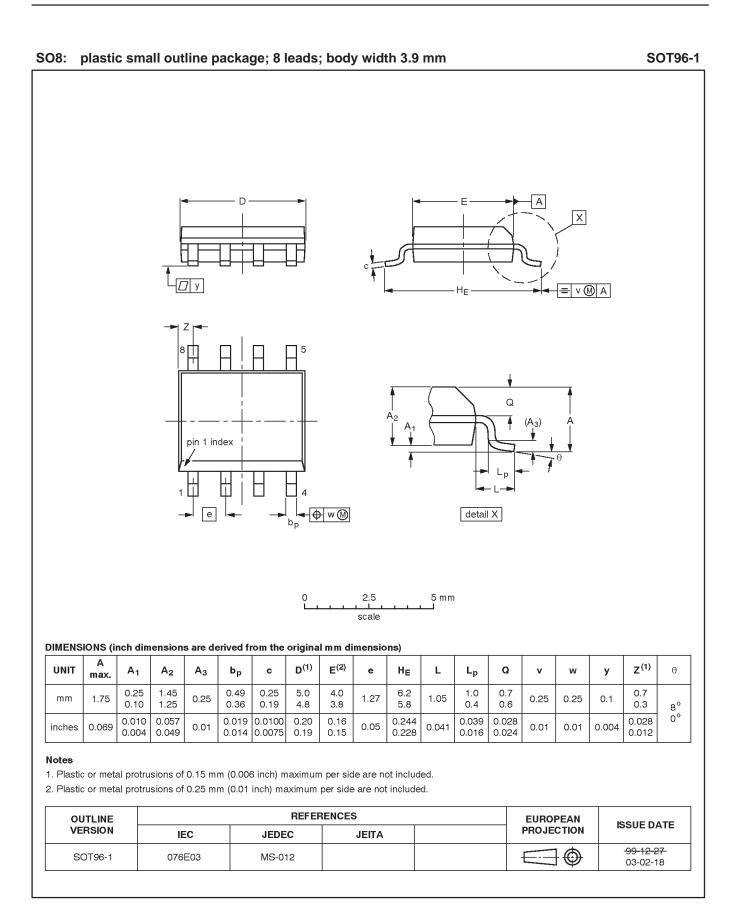

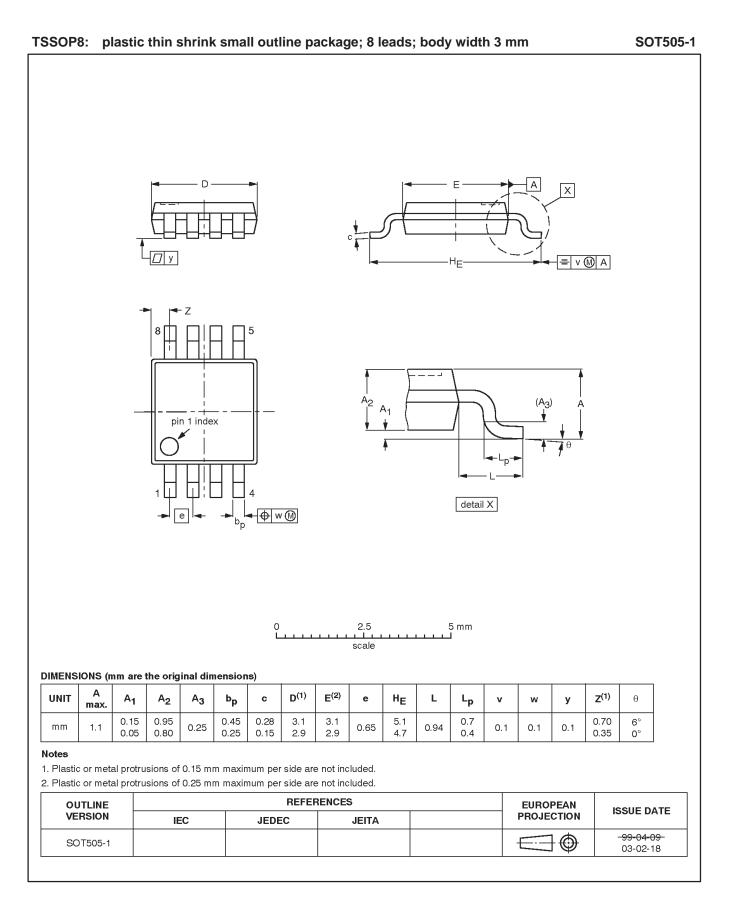

- Small 8-pin package types: SO8 and TSSOP8 (MSOP8)

- I<sup>2</sup>C-bus interface to 400kHz with up to 8 devices on the same bus

- Power supply range from 2.8 V to 5.5 V

- Temperatures range from -55 °C to +125 °C

- 13-bit ADC that offers a temperature resolution of 0.03125 °C

- Temperature accuracy of ±1 °C from -25 °C to +100 °C

- Programmable temperature threshold and hysteresis set points

- Supply current of 7.0 µA in shut-down mode for power conservation

- Stand-alone operation as thermostat at power-up

- ESD protection exceeds 1000 V HBM per JESD22-A114, 150 V MM per JESD22-A115

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

#### **APPLICATIONS**

- System thermal management

- Personal computers

- Electronics equipment

- Industrial controllers

#### ORDERING INFORMATION

| Type number | Type number Topside mark |        |                                                                        | Temperature |                   |  |

|-------------|--------------------------|--------|------------------------------------------------------------------------|-------------|-------------------|--|

| Name        |                          | Name   | Description                                                            | Version     | range             |  |

| SE95D       | SE95                     | SO8    | O8 plastic small outline package; 8 leads; body width 3.9 mm SOT96-1   |             | –55 °C to +125 °C |  |

| SE95DP      | SE95DP                   | TSSOP8 | plastic thin shrink small outline package; 8 leads;<br>body width 3 mm | SOT505-1    | –55 °C to +125 °C |  |

WATCHDOG<sup>™</sup> is a trademark of National Semiconductor Corporation.

SE95

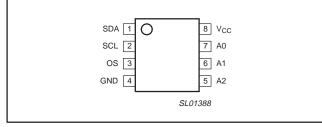

#### PINNING

#### **Pin configuration**

Figure 1. SO8 and TSSOP8 pin configurations.

Pin description

| PIN | SYMBOL          | DESCRIPTION                                                                   |

|-----|-----------------|-------------------------------------------------------------------------------|

| 1   | SDA             | Digital I/O. I <sup>2</sup> C serial bi-directional data line.<br>Open Drain. |

| 2   | SCL             | Digital input. I <sup>2</sup> C serial clock input.                           |

| 3   | OS              | Overtemp Shutdown output. Open Drain.                                         |

| 4   | GND             | Ground. To be connected to the system ground.                                 |

| 5   | A2              | Digital input. User-defined address bit2.                                     |

| 6   | A1              | Digital input. User-defined address bit1.                                     |

| 7   | A0              | Digital input. User-defined address bit0.                                     |

| 8   | V <sub>CC</sub> | Power supply.                                                                 |

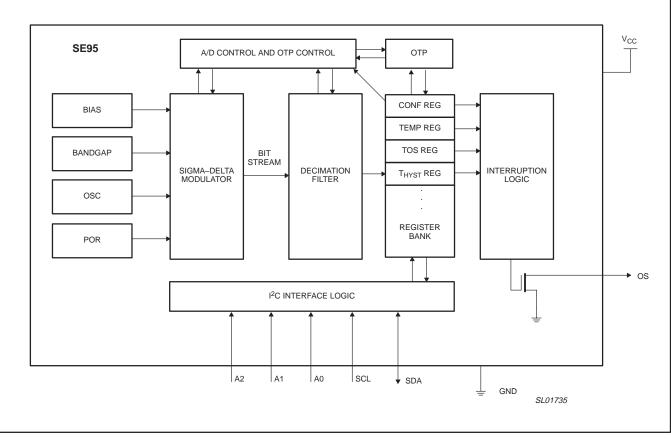

#### SIMPLIFIED BLOCK DIAGRAM

Figure 2. Simplified block diagram.

### **SE95**

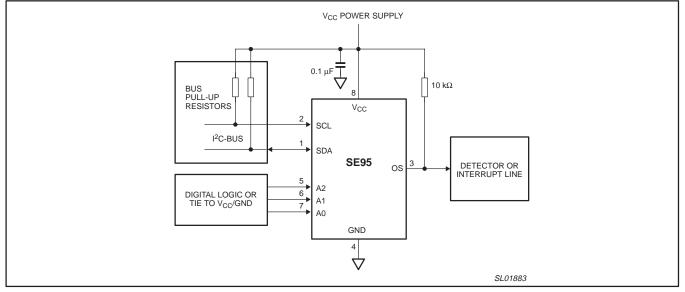

#### **TYPICAL APPLICATION CIRCUIT**

Figure 3. Typical application circuit

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL           | PARAMETER                     | MIN. | MAX.                  | UNIT |

|------------------|-------------------------------|------|-----------------------|------|

|                  | V <sub>CC</sub> to GND        | -0.3 | 6.0                   | V    |

|                  | Voltage at inputs SCL and SDA | -0.3 | 6.0                   | V    |

|                  | Voltage at inputs A0, A1, A2  | -3.0 | V <sub>CC</sub> + 0.3 | V    |

|                  | Current at input pins         | -5.0 | 5.0                   | mA   |

|                  | OS output sink current        | -    | 10.0                  | mA   |

|                  | OS output voltage             | -0.3 | 6.0                   | V    |

| V <sub>esd</sub> | Human Body Model              | -    | 1000                  | V    |

|                  | Machine Model                 | -    | 150                   | V    |

| T <sub>stg</sub> | Storage temperature range     | -65  | 150                   | °C   |

| Тj               | Junction temperature          | -    | 150                   | °C   |

NOTE:

1. This is a stress rating only. Functional operation of the device as indicated in the operational section is not applied to this absolute maximum rating. Stresses above those listed in 'Absolute Maximum Ratings' may cause permanent damage to the device and exposure to any of these rating conditions for extended periods may affect device reliability.

#### **OPERATING RATINGS**

| SYMBOL           | PARAMETER                           | MIN. | MAX. | UNIT |

|------------------|-------------------------------------|------|------|------|

| V <sub>CC</sub>  | Supply voltage                      | 2.8  | 5.5  | V    |

| T <sub>amb</sub> | Operating ambient temperature range | -55  | 125  | °C   |

# Ultra high accuracy digital temperature sensor and thermal $Watchdog^{\mbox{\tiny TM}}$

**SE95**

Product data sheet

#### **DC ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 2.8 V to 5.5 V,  $T_{amb}$  = –55  $^\circ C$  to +125  $^\circ C$  unless otherwise noted.

| SYM               | PARAMETER                          | CONDITIONS                                            | MIN.                | TYP. <sup>2</sup> | MAX.                  | UNIT              |

|-------------------|------------------------------------|-------------------------------------------------------|---------------------|-------------------|-----------------------|-------------------|

| T <sub>ACC</sub>  | Temperature accuracy (Note 1)      | $T_{amb} = -25 \ ^{\circ}C \ to +100 \ ^{\circ}C$     | -1.0                | _                 | +1.0                  | °C                |

|                   | $V_{CC} = 2.8 V \text{ to } 3.6 V$ | $T_{amb} = -55 \text{ °C to } +125 \text{ °C}$        | -2.0                | _                 | +2.0                  | °C                |

|                   | Temperature accuracy (Note 1)      | $T_{amb} = -25 \text{ °C to } +100 \text{ °C}$        | -2                  | _                 | +2                    | °C                |

|                   | $V_{CC}$ = 3.6 V to 5.5 V          | $T_{amb} = -55 \text{ °C to } +125 \text{ °C}$        | -3                  | _                 | +3                    | °C                |

| T <sub>RES</sub>  | Temperature resolution             | 11-bit digital temp data                              | _                   | 0.125             | -                     | °C                |

| T <sub>CON</sub>  | Temperature conversion time        | Normal mode                                           | -                   | 33                | -                     | ms                |

| I <sub>DD</sub>   | Supply quiescent current           | Normal mode: I <sup>2</sup> C inactive                | _                   | 150               | -                     | μA                |

|                   |                                    | Normal mode: I <sup>2</sup> C active                  | -                   | _                 | 1.0                   | mA                |

|                   |                                    | Shut-down mode                                        | _                   | 7.5               | -                     | μA                |

| VIH               | HIGH-level input voltage           | Digital pins (SCL, SDA, A2–A0)                        | $0.7 \times V_{CC}$ | _                 | V <sub>CC</sub> + 0.3 | V                 |

| V <sub>IL</sub>   | LOW-level input voltage            | Digital pins                                          | -0.3                | _                 | $0.3 \times V_{CC}$   | V                 |

| V <sub>IHYS</sub> | Input voltage hysteresis           | SCL and SDA pins                                      | -                   | 300               | -                     | mV                |

|                   |                                    | A2 to A0 pins                                         | -                   | 300               | -                     | mV                |

| I <sub>IH</sub>   | HIGH-level input current           | Digital pins; V <sub>IN</sub> = V <sub>CC</sub>       | -1.0                | _                 | 1.0                   | μA                |

| IIL               | LOW-level input current            | Digital pins; V <sub>IN</sub> = 0 V                   | -1.0                | _                 | 1.0                   | μΑ                |

| V <sub>OL</sub>   | LOW-level output voltage           | SDA and OS pins; I <sub>OL</sub> = 3 mA               | -                   | _                 | 0.4                   | V                 |

|                   |                                    | I <sub>OL</sub> = 4 mA                                | -                   | -                 | 0.8                   | V                 |

| I <sub>LO</sub>   | Output leakage current             | SDA and OS pins; $V_{OH} = V_{CC}$                    | -                   | _                 | 10                    | μA                |

| POR               | Power-on reset                     | V <sub>CC</sub> supply below which the logic is reset | 1.0                 | -                 | 2.5                   | V                 |

| OSQ               | OS fault queue                     | Programmable                                          | 1                   | _                 | 6                     | Conv <sup>3</sup> |

| Tos               | Overtemp shutdown                  | Default value                                         | -                   | 80                | -                     | °C                |

|                   | Sampling rate                      | Programmable                                          | 0.125               | 10                | 30                    | sample/s          |

| Thyst             | Hysteresis                         | Default value                                         | -                   | 75                | -                     | °C                |

| C <sub>IN</sub>   | Input capacitance                  | Digital pins                                          | -                   | 20                | -                     | pF                |

NOTE:

1. Assumes a minimum 11-bit temperature reading. 2. Typical values are at  $V_{CC} = 3.3$  V and  $T_{amb} = 25$  °C. 3. Conv: device A-to-D conversion.

SE95

Product data sheet

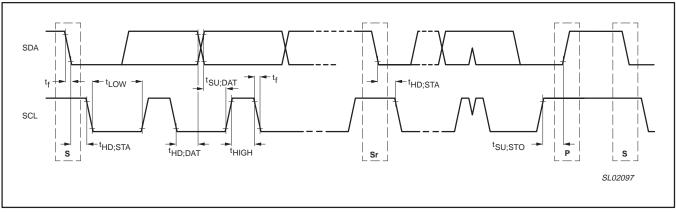

#### I<sup>2</sup>C INTERFACE AC CHARACTERISTICS<sup>1</sup>

$V_{CC}$  = 2.8 V to 5.5 V,  $T_{amb}$  = –55  $^{\circ}C$  to +125  $^{\circ}C$  unless otherwise noted.

| SYMBOL              | PARAMETER                      | CONDITIONS                                      | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------------------------------|-------------------------------------------------|------|------|------|------|

| t <sub>CLK</sub>    | SCL clock period               | See timing diagram (Figure 4)                   | 2.5  | -    | -    | μs   |

| t <sub>HIGH</sub>   | SCL HIGH pulse width           |                                                 | 0.6  | -    | -    | μs   |

| t <sub>LOW</sub>    | SCL LOW pulse width            |                                                 | 1.3  | -    | -    | μs   |

| t <sub>HD:STA</sub> | Start Hold time                |                                                 | 100  | -    | -    | ns   |

| t <sub>SU:DAT</sub> | Data set-up time               |                                                 | 100  | -    | -    | ns   |

| t <sub>HD;DAT</sub> | Data hold time                 |                                                 | 0    | -    | -    | ns   |

| t <sub>SU;STO</sub> | Stop set-up time               |                                                 | 100  | -    | -    | ns   |

| t <sub>F</sub>      | Fall time (SDA and OS outputs) | $C_{L} = 400 \text{ pF}; I_{OL} = 3 \text{ mA}$ | _    | 250  | -    | ns   |

#### NOTE:

1. These specifications are guaranteed by design and not tested in production.

Figure 4. Timing diagram.

### **SE95**

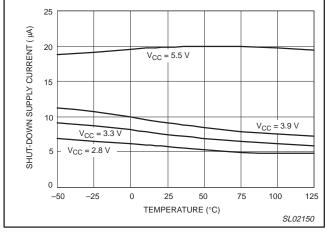

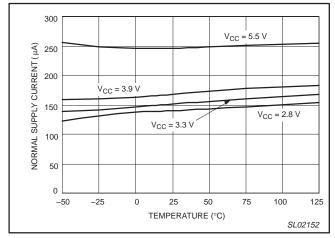

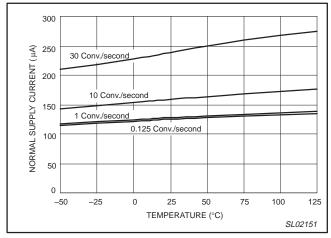

#### PERFORMANCE CURVES

Figure 5. Typical shut-down supply current versus temperature and V<sub>CC</sub>

Figure 6. Typical normal I<sup>2</sup>C inactive supply current versus temperature and V<sub>CC</sub>

Figure 7. Typical normal I<sup>2</sup>C inactive supply current versus temperature and conversion rate ( $V_{CC}$  = 3.3 V)

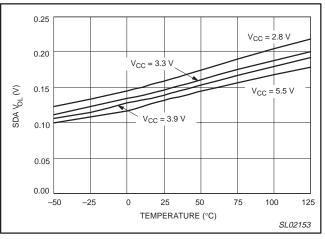

Figure 8. Typical SDA V<sub>OL</sub> versus temperature and V<sub>CC</sub> ( $I_{OL}$  = 3 mA)

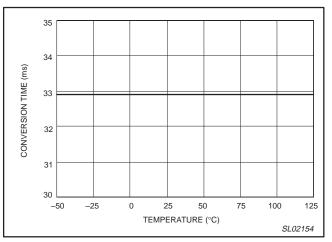

Figure 9. Typical conversion time versus temperature (V<sub>CC</sub> = 2.8 V to 5.5 V)

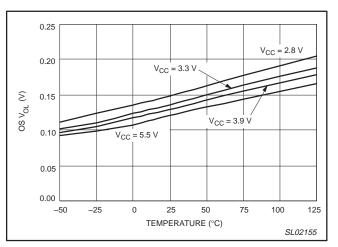

Figure 10. Typical OS V<sub>OL</sub> versus temperature and V<sub>CC</sub> ( $I_{OL}$  = 3 mA)

Product data sheet

### **SE95**

#### FUNCTIONAL DESCRIPTION

#### **General operation**

The SE95 uses the on-chip band-gap sensor to measure the device temperature with the resolution of 0.03125 °C and stores the 13-bit 2's complement digital data, resulted from 13-bit A-to-D conversion, into the device Temp register. This Temp register can be read at any time by a controller on the l<sup>2</sup>C-bus. Reading temperature data does not affect the conversion in progress during the read operation.

The device can be set to operate in either mode: normal or shut-down. In normal operation mode, by default, the temp-to-digital conversion is executed every 100 ms and the Temp register is updated at the end of each conversion. In shut-down mode, the device becomes idle, data conversion is disabled and the Temp register holds the latest result; however, the device l<sup>2</sup>C interface is still active and register write/ read operation can be performed. The device operation mode is controlled by programming bit B0 of the configuration register. The temperature conversion is initiated when the device is powered up or returned to normal mode from shut-down.

In addition, at the end of each conversion in normal mode, the temperature data (or Temp) in the Temp register is automatically compared with the over-temp shut-down threshold data (or Tos) stored in the Tos register, and the hysteresis data (or Thyst) stored in the Thyst register, in order to set the state of the device OS output accordingly. The device Tos and Thyst registers are write/read capable, and both operate with 9-bit 2's complement digital data. To match with this 9-bit operation, the temp register uses only the 9 MSB bits of its 13-bit data for the comparison.

The device temperature conversion rate is programmable and can be chosen to be one of the four values: 0.125, 1.0, 10, and 30 conversions per second. The default conversion rate is 10 conversions per second. Furthermore, the conversion rate is selected by programming bits B5 and B6 of the Configuration Register as shown in Table 3. Note that the average supply current as well as the device power consumption increase with the conversion rate. The way that the OS output responds to the comparison operation depends upon the OS operation mode selected by configuration bit B1, and the user-defined fault queue defined by configuration bits B3 and B4.

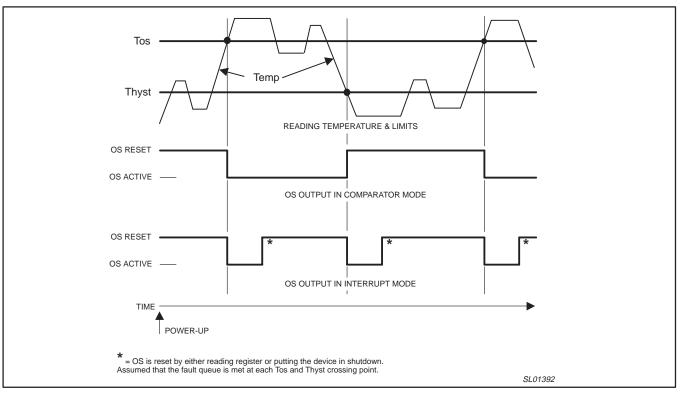

In OS comparator mode, the OS output behaves like a thermostat. It becomes active when the Temp exceeds the Tos, and is reset when the Temp drops below the Thyst. Reading the device registers or putting the device into shut-down does not change the state of the OS output. The OS output in this case can be used to control cooling fans or thermal switches.

In OS interrupt mode, the OS output is used for thermal interruption. When the device is powered-up, the OS output is first activated only when the Temp exceeds the Tos; then it remains active indefinitely until being reset by a read of any register. Once the OS output has been activated by crossing Tos and then reset, it can be activated again only when the Temp drops below the Thyst; then again, it remains active indefinitely until being reset by a read of any register. The OS interrupt operation would be continued in this sequence: Tos trip, Reset, Thyst trip, Reset, Tos trip, Reset, Thyst trip, Reset, and etc. Putting the device into shut-down mode also resets the OS output.

In both cases, comparator mode and interrupt mode, the OS output is activated only if a number of consecutive faults, defined by the device fault queue, has been met. The fault queue is programmable and stored in the two bits, B3 and B4, of the Configuration register. Also, the OS output active state is selectable as HIGH or LOW by setting accordingly the configuration register bit B2.

At power-up, the device is put into normal operation mode, the Tos is set to 80 °C, the Thyst is set to 75 °C, the OS active state is selected LOW and the fault queue is equal to 1. The temp reading data is not available until the first conversion is completed in about 33 ms.

The OS response to the temperature is illustrated in Figure 11.

**SE95**

Figure 11. OS response to temperature.

### **SE95**

#### I<sup>2</sup>C serial interface

The SE95 can be connected to a compatible 2-wire serial interface I<sup>2</sup>C-bus as a slave device under the control of a controller or master device, using two device terminals, SCL and SDA. The controller must provide the SCL clock signal and write/read data to/from the device through the SDA terminal. Note that if the I<sup>2</sup>C common pull-up resistors have not been installed as required for I<sup>2</sup>C-bus, then an external pull-up resistor, about 10 k $\Omega$ , is needed for each of these two terminals. The bus communication protocols are described in the data communication section.

#### Slave address

The SE95 slave address on the l<sup>2</sup>C-bus is partially defined by the logic applied to the device address pins A2, A1 and A0. Each pin is typically connected either to GND for logic 0, or to  $V_{CC}$  for logic 1. These pins represent the three LSB bits of the device 7-bit address. The other four MSB bits of the address data are preset to '1001' by hard wiring inside the SE95. Table 1 shows the device's complete address and indicates that up to 8 devices can be connected to the same bus without address conflict. Because the input pins, SCL, SDA, A2–A0, are not internally biased, it is important that they should not be left floating in any application.

#### Table 1. Address table

1 = HIGH, 0 = LOW

| MSB |   |   |   |    |    | LSB |

|-----|---|---|---|----|----|-----|

| 1   | 0 | 0 | 1 | A2 | A1 | A0  |

#### **Register list**

The SE95 contains 7 data registers. The registers can be 1 byte or 2 bytes wide, and are defined in Table 2. The registers are accessed by the value in the content of the pointer register during I<sup>2</sup>C-bus communication. The types of registers are: read only, read/write, and reserved for manufacturer use. Note that when reading a two-byte register, the host must provide enough clock pulses as required by the I<sup>2</sup>C protocol (see the "Data communication" section) for the device to completely return both data bytes. Otherwise the device may hold the SDA line as LOW state, resulting in a bus hang condition.

#### **Register pointer**

The register pointer or pointer byte is an 8-bit data byte that is equivalent to the register command in the  $I^2C$ -bus definitions and is used to identify the device register to be accessed for a write or read operation. Its values are listed as pointer values in Table 2, "Register table". For the device register  $I^2C$ -bus communication, the pointer byte may or may not need to be included within the command as illustrated in the  $I^2C$  protocol figures in section "Data communication" on page 14.

The command statements of writing data to a register must always include the pointer byte; while the command statements of reading data from a register may or may not include it. To read a register that is different from the one that has been recently read, the pointer byte must be included. However, to re-read a register that has been recently read, the pointer byte may not have to be included in the reading.

At power-up, the pointer value is preset to '0' for the Temp Register; users can then read the temperature without specifying the pointer byte.

#### Table 2. Register table

| Register name | Pointer value | R/W       | POR state | Description                                                                                                                                                                       |

|---------------|---------------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conf          | 01H           | R/W       | 00H       | Configuration Register.<br>Contains a single 8-bit data byte. To set an operating condition.                                                                                      |

| Temp          | 00H           | Read only | N/A       | Temperature Register.<br>Contains two 8-bit data bytes. To store the measured Temp data.                                                                                          |

| Tos           | 03H           | R/W       | 50 00H    | <b>Over-temp Shutdown threshold Register.</b><br>Contains two 8-bit data bytes. To store the over-temp shut-down Tos limit.<br>Default = $80 \degree C$ .                         |

| Thyst         | 02H           | R/W       | 4B 00H    | Hysteresis Register.<br>Contains two 8-bit data bytes. To store the hysteresis Thyst limit.<br>B7–B0 are also used in OTP test mode to supply OTP write data.<br>Default = 75 °C. |

| ID            | 05H           | Read only | A1H       | ID Register.<br>Contains a single 8-bit data byte for the manufacturer ID code.                                                                                                   |

| reserved      | 04H           | N/A       | N/A       | Reserved.                                                                                                                                                                         |

| reserved      | 06H           | N/A       | N/A       | Reserved.                                                                                                                                                                         |

SE95

#### **Configuration register**

The Configuration register is a write/read register and contains an 8-bit non-complement data byte that is used to configure the device for different operating conditions. The Configuration register table (Table 3) shows the bit assignments of this register.

| Table 3. | Configuration | register | table |

|----------|---------------|----------|-------|

|----------|---------------|----------|-------|

| Bit   | Name              | R/W | POR | Description                                                                                                                     |

|-------|-------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------|

| B7    | Reserved          | R/W | 0   | Reserved for manufacturer's use.                                                                                                |

| B6–B5 | Rate val          | R/W | 00  | Sets the conversion rate:                                                                                                       |

|       |                   |     |     | 00 = 10 conversions/sec (default)                                                                                               |

|       |                   |     |     | 01 = 0.125 conversions/sec                                                                                                      |

|       |                   |     |     | 10 = 1 conversions/sec                                                                                                          |

|       |                   |     |     | 11 = 30 conversions/sec                                                                                                         |

| B4–B3 | OS Fault queue    | R/W | 0   | For OS Fault Queue programming.<br>Programmable queue data = 0, 1, 2, 3 for queue value = 1, 2, 4, 6 respectively. Default = 0. |

| B2    | OS Polarity       | R/W | 0   | For OS Polarity selection.<br>1 = OS active HIGH, 0 = OS active LOW (default).                                                  |

| B1    | OS Comp/Interrupt | R/W | 0   | For OS operation Mode selection.<br>1 = OS interrupt, 0 = OS comparator (default).                                              |

| B0    | Shut-down         | R/W | 0   | For Device Operation Mode selection.<br>1 = Shut-down, 0 = Normal (default).                                                    |

#### Temperature Register (Temp)

The Temp register holds the digital result of temperature measurement or monitor at the end each A-to-D conversion. This register is read only and contains two 8-bit data bytes consisting of one most significant (MS) data byte and one least significant (LS) data byte. However, only 13 bits of those two bytes are used to store the Temp data in 2's complement format with the resolution of 0.03125 °C. The Temp register table (Table 4) shows the bit arrangement of the Temp data in the data bytes.

#### Table 4. Temp Register table

|     | Temp MS byte |     |            |          |    |    |     |     |    |     | Temp L | S byte |    |    |     |

|-----|--------------|-----|------------|----------|----|----|-----|-----|----|-----|--------|--------|----|----|-----|

| MSB |              |     |            |          |    |    | LSB | MSB |    |     |        |        |    |    | LSB |

| B7  | B6           | B5  | B4         | B3       | B2 | B1 | B0  | B7  | B6 | B5  | B4     | B3     | B2 | B1 | B0  |

|     |              | fo  | r 11-bit 1 | Femp Dat | ta |    |     |     |    |     | Not    | used   |    |    |     |

| MSB |              |     |            |          |    |    |     |     |    | LSB |        |        |    |    |     |

| D10 | D9           | D8  | D7         | D6       | D5 | D4 | D3  | D2  | D1 | D0  | Х      | Х      | Х  | Х  | Х   |

|     | -            | fo  | r 13-bit T | Temp Dat | ta |    |     |     |    |     | Not    | used   |    |    |     |

| MSB |              |     |            |          |    |    |     |     |    |     |        | LSB    |    |    |     |

| D12 | D11          | D10 | D9         | D8       | D7 | D6 | D5  | D4  | D3 | D2  | D1     | D0     | Х  | Х  | Х   |

When reading the Temp register, all 16 bits of the two data bytes (MS byte and LS byte) must be collected and then the 2's complement data value according to the desired resolution must be selected for the temperature calculation. The Table 4 has shown the examples for two cases: 11-bit 2's complement data value, and 13-bit 2's complement data value. When converting into the temperature the proper resolution must be used as listed in Table 5 using either one of these two formulae:

1. If the Temp Data MSB = 0, then: Temp Value ( $^{\circ}$ C) = +(Temp Data) × Value Resolution

2. If the Temp Data MSB = 1, then: Temp Value ( $^{\circ}$ C) = -(2's complement Temp Data) × Value Resolution

Table 6 shows some examples of the results for the 11-bit calculations.

#### Table 5. Temp Data and Temp Value resolution

| Data resolution | Value resolution |

|-----------------|------------------|

| 8 bits          | 1.0 °C           |

| 9 bits          | 0.5 °C           |

| 10 bits         | 0.25 °C          |

| 11 bits         | 0.125 °C         |

| 12 bits         | 0.0625 °C        |

| 13 bits         | 0.03125 °C       |

### **SE95**

|                                | Temp data |               |             |  |  |  |  |  |  |

|--------------------------------|-----------|---------------|-------------|--|--|--|--|--|--|

| 11-bit Binary (2's complement) | 3-bit Hex | Decimal value | ٥C          |  |  |  |  |  |  |

| 0111 1111 000                  | 3F8h      | 1016          | +127.000 °C |  |  |  |  |  |  |

| 0111 1110 111 3F7h             |           | 1015          | +126.875 °C |  |  |  |  |  |  |

| 0111 1110 001                  | 3F1h      | 1009          | +126.125 °C |  |  |  |  |  |  |

| 0111 1101 000                  | 3E8h      | 1000          | +125.000 °C |  |  |  |  |  |  |

| 0001 1001 000                  | 0C8h      | 200           | +25.000 °C  |  |  |  |  |  |  |

| 0000 0000 001 001h             |           | 1             | +0.125 °C   |  |  |  |  |  |  |

| 0000 0000 000 000h             |           | 0             | 0.000 °C    |  |  |  |  |  |  |

| 1111 1111 111 7FFh             |           | -1            | –0.125 °C   |  |  |  |  |  |  |

| 1110 0111 000 738h             |           | -200          | –25.000 °C  |  |  |  |  |  |  |

| 11001001 001                   | 649h      | -439          | –54.875 °C  |  |  |  |  |  |  |

| 1100 1001 000                  | 648h      | -440          | –55.000 °C  |  |  |  |  |  |  |

#### Table 6. Temp table

Obviously, for 9-bit Temp data application in replacing the industry standard LM75, just use only 9 MSB bits of the two bytes and disregard 7 LSB bits of the LS byte. The 9-bit temp data with 0.5 °C resolution of the SE95 is defined exactly in the same way as for the standard LM75 and it is here similar to the Tos and Thyst that is described next.

#### Overtemp shut-down threshold (Tos) and hysteresis (Thyst) registers

These two registers are write/read registers, and also called set-point registers. They are used to store the user-defined temperature limits, called overtemp shut-down threshold (Tos) and hysteresis (Thyst), for the device Watchdog operation. At the end of each conversion the Temp data will be compared with the data stored in these two registers in order to set the state of the device OS output accordingly as described in the "General operation" section.

Each of the set-point registers contains two 8-bit data bytes consisting of one MS data byte and one LS data byte the same as the Temp register. However, only 9 bits of the two bytes are used to store the set-point data in 2's complement format with the resolution of 0.5 °C. The Tos register table (Table 7) and Thyst register table (Table 8) show the bit arrangement of the Tos data and Thyst data in the data bytes.

Notice that because only 9-bit data are used in the set-point registers, the device uses only the 9 MSB bits of the Temp data for data comparison.

#### Table 7. Tos register table

|     | Tos MS byte       |    |    |    |    |    |     |     |    |    | Tos L    | S byte |    |    |     |

|-----|-------------------|----|----|----|----|----|-----|-----|----|----|----------|--------|----|----|-----|

| MSB |                   |    |    |    |    |    | LSB | MSB |    |    |          |        |    |    | LSB |

| B7  | B6                | B5 | B4 | B3 | B2 | B1 | B0  | B7  | B6 | B5 | B4       | B3     | B2 | B1 | B0  |

|     | Tos data (9 bits) |    |    |    |    |    |     |     |    | l  | Not used | l      |    |    |     |

| MSB |                   |    |    |    |    |    |     | LSB |    |    |          |        |    |    |     |

| D8  | D7                | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Х  | Х  | Х        | Х      | Х  | Х  | Х   |

#### Table 8. Thyst register table

|     | Thyst MS byte       |    |    |    |    |    |     |     |    |    | Thyst L  | S byte |    |    |     |

|-----|---------------------|----|----|----|----|----|-----|-----|----|----|----------|--------|----|----|-----|

| MSB |                     |    |    |    |    |    | LSB | MSB |    |    |          |        |    |    | LSB |

| B7  | B6                  | B5 | B4 | B3 | B2 | B1 | B0  | B7  | B6 | B5 | B4       | B3     | B2 | B1 | B0  |

|     | Thyst data (9 bits) |    |    |    |    |    |     |     |    | I  | Not used | I      |    |    |     |

| MSB |                     |    |    |    |    |    |     | LSB |    |    |          |        |    |    |     |

| D8  | D7                  | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Х  | Х  | Х        | Х      | Х  | Х  | Х   |

When a set-point register is read, all 16 bits are provided to the bus and must be collected by the controller to complete the bus operation. However, only the 9 significant bits should be used and the 7 LSB bits of the LS byte are equal to zero and should be ignored.

The Tos and Thyst table (Table 9) shows examples of the limit data and value.

Product data sheet

**SE95**

| Table 9. Tos and Thyst table | Table | 9. | Tos | and | Thyst | table |

|------------------------------|-------|----|-----|-----|-------|-------|

|------------------------------|-------|----|-----|-----|-------|-------|

|                                | Limit data |               |           |  |  |  |  |  |

|--------------------------------|------------|---------------|-----------|--|--|--|--|--|

| 11-bit Binary (2's complement) | 3-bit Hex  | Decimal value | °C        |  |  |  |  |  |

| 0111 1101 0                    | 0FAh       | 250           | +125.0 °C |  |  |  |  |  |

| 0001 1001 0                    | 032h       | 50            | +25.0 °C  |  |  |  |  |  |

| 0000 0000 1                    | 001h       | 1             | +0.5 °C   |  |  |  |  |  |

| 0000 0000 0                    | 000h       | 0             | 0.0 °C    |  |  |  |  |  |

| 1111 1111 1                    | 1FFh       | -1            | −0.5 °C   |  |  |  |  |  |

| 1110 0111 0                    | 1CEh       | -50           | −25.0 °C  |  |  |  |  |  |

| 1100 1001 0                    | 192h       | -110          | −55.0 °C  |  |  |  |  |  |

#### OS output and polarity

The OS output is an open-drain output and its state represents results of the device Watchdog operation as described in the "General operation" section. In order to observe this output state, an external pull-up resistor is needed. The resistor should be as large as possible, up 200 k $\Omega$ , to minimize the temp reading error due to internal heating by the high OS sinking current.

The OS output active state can be selected as HIGH or LOW by programming bit B2 of the Configuration register: setting B2 to 1 selects OS active HIGH and setting B2 to 0 sets OS active LOW. At power-up, this bit is equal to 0 and the OS active state is LOW.

#### OS comparator and interrupt modes

As described in the "General operation" section, the device OS output responds to the result of the comparison between the Temp data and the programmed limits, Tos and Thyst, in different ways depending on the selected OS mode: OS comparator or OS interrupt. The OS mode is selected by programming bit B1 of the configuration register: setting B1 to 1 selects the OS interrupt mode, and setting B1 to 0 selects the OS comparator mode. At power up, this bit is equal to 0 and the OS comparator is selected.

The main difference between the two modes is that in OS comparator mode, the OS output becomes active when the Temp has exceeded the Tos and reset when the Temp has dropped below the Thyst, reading a register or putting the device into shut-down does not change the state of the OS output; while in OS interrupt mode, once it has been activated either by exceeding the Tos or dropping below the Thyst, the OS output will remain active indefinitely until reading a register or putting the device into shut-down occurs, then the OS output is reset.

The Tos & Thyst limits must be selected so that Tos temp value > Thyst temp value. Otherwise, the OS output state will be undefined.

#### OS fault queue

Fault queue is defined as the number of faults that must occur consecutively to activate the OS output. It is provided to avoid false tripping due to noise. Because faults are determined at the end of data conversions, fault queue is also defined as the number of consecutive conversions returning a temperature trip. The value of fault queue is selectable by programming the two bits B4 and B3 of

the configuration register. Notice that the programmed data and the fault queue value are not the same. The Fault queue table (Table 10) shows the one-to-one relationship between them. At power-up, fault queue data = 0 and fault queue value = 1.

#### Table 10. Fault queue table

| Fault que | eue data | Fault queue value |

|-----------|----------|-------------------|

| B4        | B3       | Decimal           |

| 0         | 0        | 1                 |

| 0         | 1        | 2                 |

| 1         | 0        | 4                 |

| 1         | 1        | 6                 |

#### Shutdown mode

The device operation mode is selected by programming bit B0 of the Configuration register: Setting B0 to 1 will put the device into shut-down mode. Resetting B0 to 0 will return the device to normal mode.

In shut-down mode, the device draws a small current of about 7.5  $\mu A$  and the power dissipation is minimized; the temperature conversion stops, but the  $l^2 C$  interface remains active and register write/read operation can be performed. If the OS output is in comparator mode, then it remains unchanged. In Interrupt mode, the OS output is reset.

#### Power-up default and Power-on Reset

The SE95 always powers-up in its default state with:

- Normal operation mode

- OS comparator mode

- − Tos = 80 °C

- − Thyst = 75 °C

- OS output active state = LOW

- Pointer value = 0.

When the power supply voltage is dropped below the device power-on reset level of about 1.9 V (POR) and then rises up again, the device will be reset to its default condition as listed above.

### SE95

#### Data communication

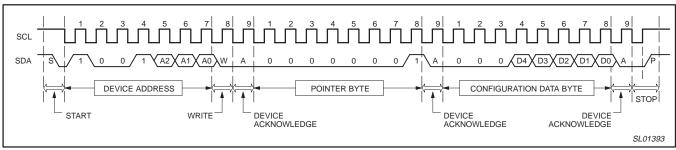

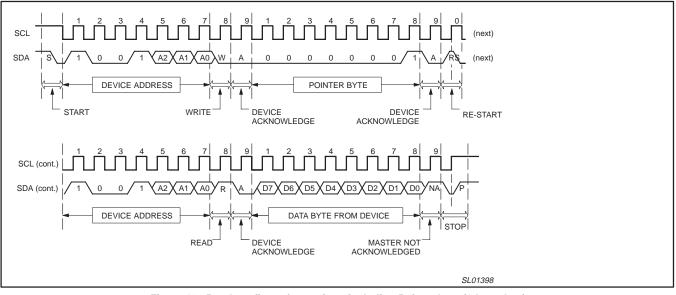

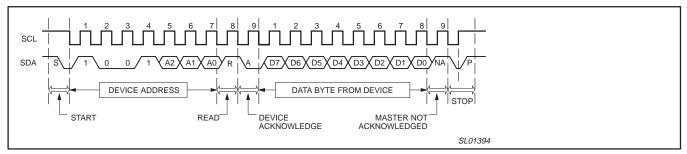

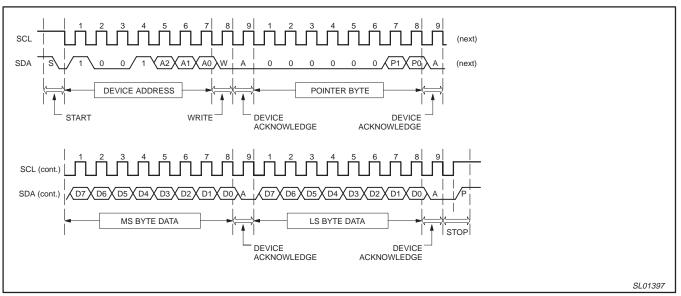

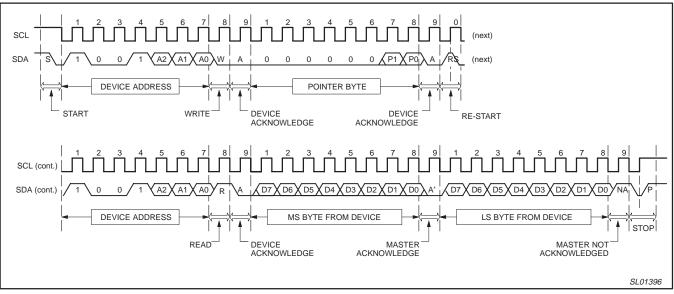

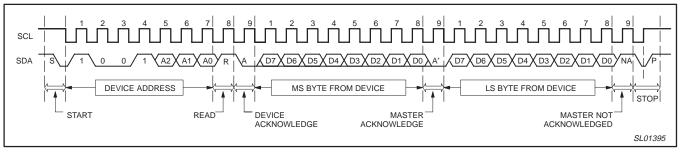

The communication between the host and the SE95 must strictly follow the rules as defined by the I<sup>2</sup>C-bus management. The protocols for SE95 register read/write operations are illustrated by the Figures as follows with these definitions:

- Before a communication, the I<sup>2</sup>C-bus must be free or not busy. It means that the SCL and SDA lines must be both released by all devices on the bus, and they become HIGH by the bus pull-up resistors.

- The host must provide SCL clock pulses necessary for the communication. Data is transferred in sequence of 9 SCL clock pulses for every 8-bit data byte followed by 1-bit status of the acknowledgement.

- During data transfer, except the Start and Stop signals, the SDA signal must be stable while the SCL signal is HIGH. It means that SDA signal can be changed only during the LOW duration of the SCL line.

- 4. **S:** Start signal, initiated by the host to start a communication, the SDA goes from HIGH-to-LOW while the SCL is HIGH.

- 5. **RS:** Re-start signal, same as the Start signal, to start a read command that follows a write command.

- 6. **P:** Stop signal, generated by the host to stop a communication, the SDA goes from LOW-to-HIGH while the SCL is HIGH. The bus becomes free thereafter.

- 7. W: Write bit, when the Write/Read bit = LOW in a write command.

- 8. **R:** Read bit, when the Write/Read bit = HIGH in a read command.

- 9. A: Device Acknowledge bit, returned by the SE95. It is LOW if the device works properly and HIGH if not. The host must release the SDA line during this period in order to give the device the control on the SDA line.

- 10. A': Master Acknowledge bit, not returned by the device, but set by the master or host in reading 2-byte data. During this clock period, the host must set the SDA line to LOW in order to notice the device that the first byte has been read for the device to provide the second byte onto the bus.

- 11. NA: Not-Acknowledge bit. During this clock period, both the device and host release the SDA line at the end of a data transfer, the host is then enabled to generate the Stop signal.

- 12. In a write protocol, data is sent from the host to the device and the host controls the SDA line, except during the clock period when the device sends to the bus the device acknowledgement signal.

- 13. In a read protocol, data is sent to the bus by the device and the host must release the SDA line during the time that the device is providing data onto the bus and controlling the SDA line, except during the clock period when the master sends to the bus the master acknowledgement signal.

SE95

### Protocols for writing and reading the registers

Figure 12. Write configuration register (1-byte data).

Figure 13. Read configuration register including Pointer byte (1-byte data).

Figure 14. Read configuration register with preset Pointer (1-byte data).

SE95

Figure 15. Write Tos or Thyst register (2-byte data).

Figure 16. Read Temp or Tos or Thyst register including Pointer byte (2-byte data).

Figure 17. Read Temp or Tos or Thyst register with preset Pointer (2-byte data).

SE95

Product data sheet

\_\_\_\_

Product data sheet

SE95

Product data sheet

SE95

### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _3  | 20041221 | <ul> <li>Product data sheet (9397 750 14388). Supersedes data of 2004 Oct 05 (9397 750 14163).</li> <li>Modifications:</li> <li>'Features' section on page 2,</li> <li>2<sup>nd</sup> bullet: add "(MSOP8)" as package name variant for TSSOP8</li> <li>3<sup>rd</sup> bullet: changed from "I<sup>2</sup>C-bus interface with up to 8 devices on the same bus" to "I<sup>2</sup>C-bus interface to</li> </ul>               |

|     |          | <ul> <li>400 kHz with up to 8 devices on the same bus"</li> <li>8<sup>th</sup> bullet: changed from " from 0 °C to +100 °C" to " from -25 °C to +100 °C"</li> <li>12<sup>th</sup> bullet changed from " 100 V MM per JESD22-A115" to " 150 V MM per JESD22-A115"</li> <li>'Absolute maximum ratings' table on page 4: changed V<sub>esd</sub> Machine Model (max.) from '100 V' to '150 V'</li> </ul>                        |

|     |          | <ul> <li>'DC electrical characteristics' table on page 5:</li> <li>Symbol T<sub>ACC</sub>:<br/>replaced "(assumes a minimum 11-bit temperature reading)" with "(Note 1)"<br/>Conditions for V<sub>CC</sub> = 2.8 V to 3.6 V:<br/>changed "T<sub>amb</sub> = -25 °C to 100 °C" to "T<sub>amb</sub> = -25 °C to +100 °C"<br/>changed "T<sub>amb</sub> = -55 °C to -125 °C" to "T<sub>amb</sub> = -55 °C to +125 °C"</li> </ul> |

| _2  | 20041005 | Objective data sheet (9397 750 14163). Supersedes data of 2003 Oct 02 (9397 750 10265).                                                                                                                                                                                                                                                                                                                                      |

| _1  | 20031002 | Objective data (9397 750 10265)                                                                                                                                                                                                                                                                                                                                                                                              |

**SE95**

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: 4

Fax: **+31 40 27 24825**

© Koninklijke Philips Electronics N.V. 2004 All rights reserved. Published in the U.S.A.

Date of release: 12-04

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document number:

9397 750 14388

Let's make things better.