M56710FP

# F2F Magnetic Stripe Encoding Card Reader

REJ03F0175-0201 Rev.2.01 Mar 31, 2008

## Description

The M56710FP is a semiconductor integrated circuit of Bi-CMOS structure having an F2F demodulator function for magnetic card reader.

## Features

- Low current dissipation (0.7 mA when on standby as a standard)

- Provided with glance-over selection input (4, 8, and 16 bits)

- Provided with output polarity ("L" active or "H" active) switching input

- Miniature mini-mold package

- Wide operating temperature range Ta = -20 to  $75^{\circ}C$

# Application

Magnetic card reader

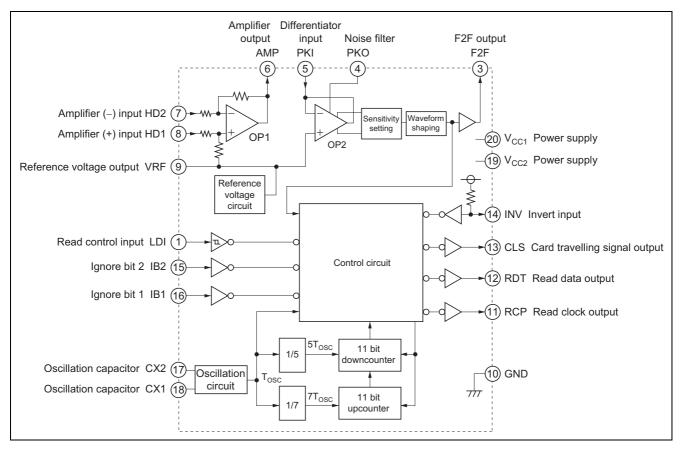

# **Functional Description**

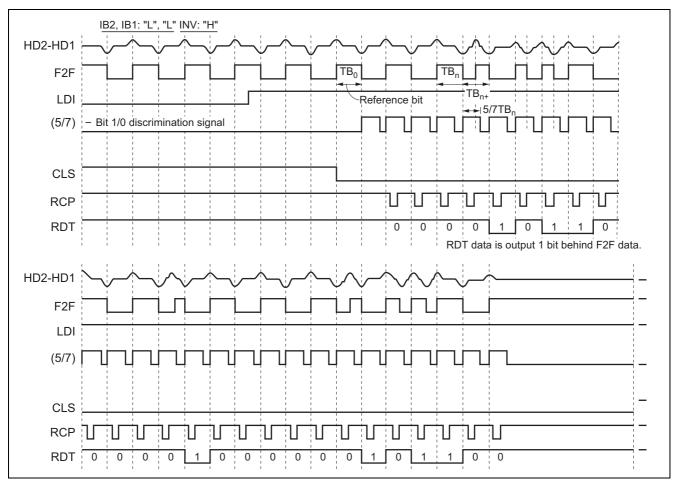

Data signal which is read from magnetic card via magnetic head is input from HD2 and HD1 pins., and converted into F2F pattern signal by analog processing in amplifier OP1, differentiator OP2, sensitivity setting circuit and waveform shaping circuit. If F2F signal is input, the logic section glances over the prescribed number of bits set by IB1 and IB2 input before performing digital processing, and then outputs card reading signal CLS, read clock signal RCP, and read data signal RDT. INV turning to "L" switches each output of CLS. RCP and RDT from "L" active to "H" active.

• Standard Bits:

Let the number of glance-over bits set by IB1 and IB2 be M.

Let the Mth FC (flux change) through M+1st FC after LDI input is turned from "L" to "H" be a standard bit with a time width of TB0.

I/O is discriminated from the next bit to this standard bit as a data bit.

• I/O discrimination

Let the data bit time width of a data bit be TBn, and if there is one next FC between the FC at the end of that bit (i.e. the beginning of the next bit) to 5/7TBn, let the next bit (Bn+1) be data "1", and, if there is no FC, be data "0".

• Output signal time width

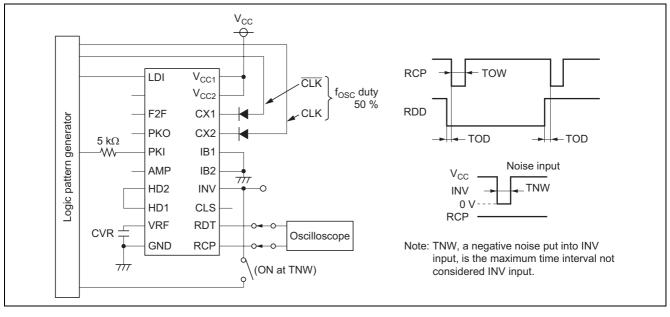

When letting the oscillation cycle of oscillation circuit be  $T_{\mbox{\scriptsize OSC}}.$

- RCP output pulse width TOW: about 16  $T_{\rm OSC}$

- RCP delay time to RDT: about 8  $T_{\rm OSC}$

# **Block Diagram**

## **Pin Arrangement**

|                         | _                   | M56710FP       | _                    |                                  |

|-------------------------|---------------------|----------------|----------------------|----------------------------------|

| Read control input      | $LDI \rightarrow 1$ | $\bigcirc$     | 20 V <sub>CC1</sub>  | Power supply                     |

|                         | NC 2                |                | 19 V <sub>CC2</sub>  | Power supply                     |

| F2F output              | F2F ← 3             |                | 18 CX1               | Oscillation capacitor            |

| Noise filter            | PKO 4               |                | 17 CX2               | Oscillation capacitor            |

| Differentiator input    | $PKI \rightarrow 5$ |                | 16 ← IB1             | Ignore bit 1                     |

| Amplifier output        | $AMP \leftarrow 6$  |                | 15 ← IB2             | Ignore bit 2                     |

| Amplifier (–) input     | HD2 $\rightarrow$ 7 |                | 14 ← INV             | Invert input                     |

| Amplifier (+) input     | $HD1 \rightarrow 8$ |                | 13 $\rightarrow$ CLS | Card travelling<br>signal output |

| Standard voltage output | VRF 9               |                | 12 $\rightarrow$ RDT | Read data output                 |

| Grounding               | GND 10              |                | 11 $\rightarrow$ RCP | Read clock output                |

|                         | L                   | (Top view)     | NC: no conr          | nection                          |

|                         | Outline: P          | RSP0020DA-A (2 | 20P2N-A)             |                                  |

RENESAS

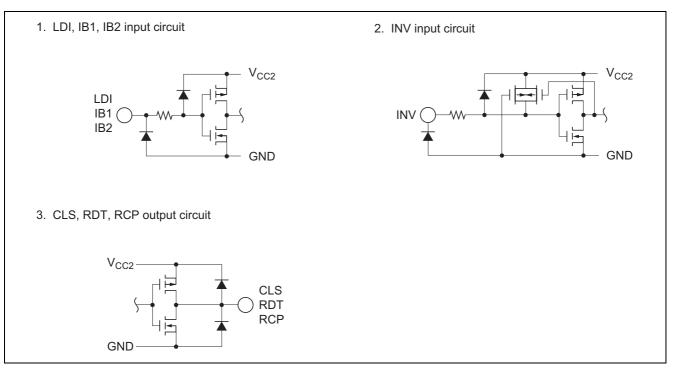

# I/O Circuit

# **Pin Function Description**

| Pin | Pin              |                               |                                                                                                            |

|-----|------------------|-------------------------------|------------------------------------------------------------------------------------------------------------|

| No. | Name             | Name                          | Function                                                                                                   |

| 1   | LDI              | Read control input            | Schmidt trigger input. At "L", reset the internal digital circuit. At "H", F2F modulation is possible.     |

| 3   | F2F              | F2F output                    | F2F signal output that has amplified, differentiated and further waveform-shaped the magnetic head signal. |

| 4   | PKO              | Noise filter                  | Connect noise removing capacitor CNF between PKI and PKO.                                                  |

| 5   | PKI              | Differentiator input          | Refer to PKO and AMP.                                                                                      |

| 6   | AMP              | Amplifier output              | Connect resistor RPK and capacitor CPK between AMP and PKI.                                                |

| 7   | HD2              | Amplifier (–) input           | Connect magnetic head between HD1 and HD2.                                                                 |

| 8   | HD1              | Amplifier (+) input           | Connect magnetic head between HD1 and HD2.                                                                 |

| 9   | VRF              | Reference voltage output      | Reference voltage output of V <sub>CC</sub> 1/2                                                            |

| 10  | GND              | Grounding                     |                                                                                                            |

| 11  | RCP              | Read clock output             | Clock pulse output after F2F modulation                                                                    |

| 12  | RDT              | Read data output              | Data output after F2F modulation                                                                           |

| 13  | CLS              | Card travelling signal output | Signal output indicating that card is travelling                                                           |

| 14  | INV              | Invert input                  | CLS, RDT and RCP output becomes "L" active at "H" (OPEN), and "H" active at "L".                           |

| 15  | IB2              | Ignore bit 2                  | Glance-over bit setting pin                                                                                |

| 16  | IB1              | Ignore bit 1                  | Glance-over bit setting pin                                                                                |

| 17  | CX2              | Oscillation capacitor         | Connect capacitor $C_{OSC}$ between CX1 and CX2 to set oscillation frequency.                              |

| 18  | CX1              | Oscillation capacitor         | Connect capacitor $C_{OSC}$ between CX1 and CX2 to set oscillation frequency.                              |

| 19  | V <sub>CC2</sub> | Power supply                  | Digital circuit section power supply pin. Supply voltage is $V_{CC}$ .                                     |

| 20  | V <sub>CC1</sub> | Power supply                  | Analog circuit section power supply pin. Supply voltage is $V_{CC}$ (same voltage as $V_{CC2}$ ).          |

RENESAS

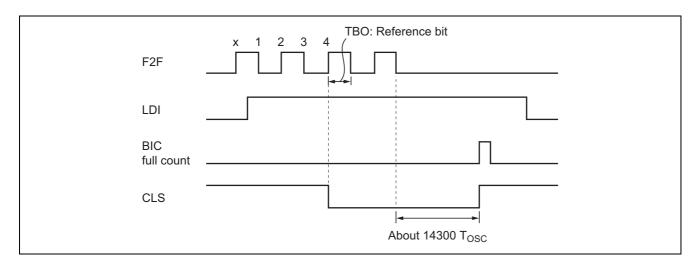

# Glance-Over Bit Setting and Timing By IB1 and IB2

|           |           | Number of<br>glance- |                                                                                                                                                                                                                   |

|-----------|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IB2 input | IB1 input | over bits            | Description                                                                                                                                                                                                       |

| L         | L         | 4                    | Internal digital circuit is reset with LDI input at "L".                                                                                                                                                          |

| L         | Н         | 8                    | LDI input may be at "H" at all times.                                                                                                                                                                             |

| H         | L         | 16                   | CLS output turns to "L" after counting the flux change FC (change in the status of F2F) of the number of glance-over bits, and returns to "H" when BIC (bit interval counter) has fully counted. (At "L" active). |

| Н         | Н         |                      | —                                                                                                                                                                                                                 |

Note: IB2, IB1 : "L", "L"

# **Operating Timing Diagram**

# **Absolute Maximum Ratings**

$(Ta = -20 \text{ to } 75^{\circ}C, \text{ unless otherwise noted})$

| Item                       | Symbol          | Ratings                            | Unit | Conditions                          |

|----------------------------|-----------------|------------------------------------|------|-------------------------------------|

| Supply voltage             | V <sub>CC</sub> | -0.3 to +6.5                       | V    | V <sub>CC1</sub> , V <sub>CC2</sub> |

| Input voltage              | VI              | –0.3 to $V_{\text{CC}}\text{+}0.3$ | V    | LDI, IB1, IB2, INV                  |

| Input voltage              | VI              | –0.3 to $V_{\text{CC}}\text{+}0.3$ | V    | HD1, HD2                            |

| Output voltage             | lo              | -10 to +10                         | mA   | CLS, RDT, RCP                       |

| Differential input voltage | V <sub>ID</sub> | -1.2 to +1.2                       | V    | Between HD2 and HD1 pins            |

| Operating temperature      | Topr            | -20 to 75                          | °C   |                                     |

| Storage temperature        | Tstg            | -55 to 125                         | °C   |                                     |

Notes: 1. Voltage is based on GND pin of the circuit (0 V), unless otherwise noted.

2. Direction of the current flowing into the circuit is represented by "positive" (without code) and that flowing out of the circuit by "negative" (-code).

# **Recommended Operating Conditions**

| (Ta                        |                                     |                 |                    |       |             |       | to 75°C, unless otherwise noted)                          |

|----------------------------|-------------------------------------|-----------------|--------------------|-------|-------------|-------|-----------------------------------------------------------|

|                            |                                     |                 | Limits             |       |             |       |                                                           |

| Item                       |                                     | Symbol          | Min                | Тур   | Max         | Unit  | Test Conditions                                           |

| Supply voltage             | $V_{CC1}, V_{CC2}$                  | V <sub>cc</sub> | 4.0                | 5     | 5.5         | V     | $V_{CC1}$ and $V_{CC2}$ shall have the identical voltage. |

| Input voltage              | LDI                                 | VI              | 0                  | —     | Vcc         | V     |                                                           |

| "H" input voltage          | IB1, IB2, INV                       | VIH             | 0.8V <sub>CC</sub> | —     | Vcc         | V     |                                                           |

| "L" input voltage          | IB1, IB2, INV                       | VIL             | 0                  | —     | $0.2V_{CC}$ | V     |                                                           |

| "H" output<br>current      | CLS, RDT,<br>RCP                    | I <sub>OH</sub> | -0.5               | _     | 0           | mA    |                                                           |

| "L" output current         | CLS, RDT,<br>RCP                    | I <sub>OL</sub> | 0                  | _     | 5           | mA    |                                                           |

| Differential input voltage | HD2-HD1                             | V <sub>IN</sub> | 3                  | _     | 80          | mVp-p |                                                           |

| Input frequency            | HD2-HD1                             | f <sub>IN</sub> | 0.3                | —     | 15          | kHz   |                                                           |

| Oscillation<br>frequency   |                                     | fosc            | 0.2                | _     | 2           | MHz   | $f_{OSC} = 1/T_{OSC}$                                     |

| External capacitor         | CX1, CX2                            | Cosc            | 25                 | —     | 100         | pF    | $f_{OSC} \propto 1/C_{OSC}$                               |

| External capacitor         | CX1, CX2                            | Cosc            | —                  | 33    | _           | pF    | Reference value when<br>corresponding to 210BPI           |

| External resistor          | AMP                                 | R <sub>РК</sub> | —                  | 470   | _           | Ω     | Reference value when<br>corresponding to 210BPI           |

| External capacitor         | PKI                                 | Срк             | —                  | 0.033 |             | μF    | Reference value when<br>corresponding to 210BPI           |

| External<br>capacitor      | PKI, PKO                            | $C_{NF}$        | —                  | 220   | _           | pF    | Reference value                                           |

| External resistor          | PKI, F2F                            | R <sub>PF</sub> | —                  | 4.7   |             | MΩ    | Reference value                                           |

| External capacitor         | V <sub>CC1</sub> , V <sub>CC2</sub> | C <sub>VC</sub> | —                  | 0.1   |             | μF    | Reference value                                           |

| External capacitor         | VRF                                 | C <sub>VR</sub> | 0.8                | 1     | 2           | μF    | Reference value                                           |

# **Electrical Characteristics**

| $(Ta = -20 \text{ to } 75^{\circ}C, V_{CC})$ | = 5 V, unless otherwise noted) |

|----------------------------------------------|--------------------------------|

|----------------------------------------------|--------------------------------|

|                                      |                       |                 | Test        |                    | Limits | 1                  |        | , unless other wise noted)                              |

|--------------------------------------|-----------------------|-----------------|-------------|--------------------|--------|--------------------|--------|---------------------------------------------------------|

| lter                                 | n                     | Symbol          | Circ<br>uit | Min                | Тур    | Max                | Unit   | Test Conditions                                         |

| Threshold                            | IB1, IB2,             | VTH             |             | 0.3V <sub>CC</sub> |        | 0.7V <sub>CC</sub> | V      | $V_{CC} = 4$ to 5.5 V                                   |

| voltage                              | INV                   |                 |             |                    |        |                    |        |                                                         |

| "L" output                           | CLS, RDT,             | V <sub>OL</sub> | 2           |                    | —      | 0.2                | V      | $V_{CC} = 4 \ V \qquad I_{OL} = 10 \ \mu A$             |

| voltage                              | RCP                   |                 | 2           |                    |        | 0.4                | V      | $I_{OL} = 5 \text{ mA}$                                 |

| "H" output                           | CLS, RDT,             | V <sub>OH</sub> | 2           | 3.8                |        |                    | V      | $V_{CC} = 4 V \qquad I_{OH} = -10 \ \mu A$              |

| voltage                              | RCP                   |                 | 2           | 3.2                | —      | —                  | V      | I <sub>OH</sub> = -0.5 mA                               |

| "L" input                            | LDI, IB1,             | IIL             | 2           | -10                | —      | +10                | μΑ     | $V_{CC} = 5.5 \ V, \ V_I = 0 \ V$                       |

| current                              | IB2                   |                 |             |                    |        |                    |        |                                                         |

| "L" input<br>current                 | INV                   | IIL             | 2           | -80                | —      | -10                | mA     | $V_{CC} = 5.5 V, V_I = 0 V$                             |

| "H" input<br>current                 | LDI, IB1,<br>IB2, INV | IIH             | 2           | -10                | _      | +10                | μΑ     | $V_{CC} = 5.5 \text{ V}, \text{ V}_{I} = 5.5 \text{ V}$ |

| Positive<br>threshold<br>current     | INV                   | IIT+            | 2           | -250               | —      | -50                | μA     | $V_{CC} = 5.5 \text{ V}, \text{ V}_{I} = \text{VTH}$    |

| Reference voltage                    | VRF                   | VREF            | 1           | 2.3                | 2.5    | 2.7                | V      | $V_{IN} = 0 mVp-p$                                      |

| Voltage gain 1                       | OP1                   | GV11            | 3           | 18                 | 20     | 24                 | Double | f <sub>IN</sub> = 1 kHz                                 |

|                                      |                       |                 |             |                    |        |                    |        | $V_{IN} = 80 \text{ mVp-p}$ sine wave                   |

| Voltage gain 2                       | OP1                   | GV21            | 3           | 18                 | 20     | 24                 | Double | f <sub>IN</sub> = 15 kHz                                |

|                                      |                       |                 |             |                    |        |                    |        | V <sub>IN</sub> = 80 mVp-p sine wave                    |

| Input                                | OP1                   | RIN1            | 3           | 7                  | 10     | 14                 | kΩ     | f <sub>IN</sub> = 1 kHz                                 |

| resistance                           | 0.54                  | 100004          |             | -                  |        |                    |        | $V_{IN} = 80 \text{ mVp-p sine wave}$                   |

| Maximum<br>output voltage            | OP1                   | VOPP1           | 3           | 2                  |        | _                  | Vр-р   | f <sub>IN</sub> = 1 kHz sine wave<br>THD AMP = 5%       |

| "L" sensitivity                      | PKI – F2F             | IIL2            | 4           | _                  |        | -0.3               | μA     | VM, F2F < 0.5 V                                         |

| current                              |                       |                 |             |                    |        |                    |        |                                                         |

| "H" sensitivity<br>current           | PKI – F2F             | IIH2            | 4           | 0.3                | —      | —                  | μΑ     | VM, F2F > 4.5 V                                         |

| Positive<br>threshold<br>voltage     | PKI – F2F             | VTH+2           | 5           | 0.2                | 0.45   | 0.7                | V      | On the VRF basis                                        |

| Negative<br>threshold<br>voltage     | PKI – F2F             | VTH-2           | 5           | -0.7               | -0.45  | -0.2               | V      | On the VRF basis                                        |

| Threshold<br>differential<br>voltage | PKI – F2F             | VTHD2           | _           | -0.15              | —      | 0.15               | V      | (VTH+2) –  VTH–2                                        |

| Pin voltage<br>range                 | РКО                   | VPKO            | 4           | -1.2               | _      | 1.2                | V      | On the VRF basis<br> PK  = 1 mA - +1 mA                 |

| "L" output<br>voltage                | F2F                   | VOL3            | 5           |                    | —      | 0.5                | V      | VPKI = 0 V, IF2F = 0.5 mA                               |

| "H" output<br>voltage                | F2F                   | VOH3            | 5           | 4.5                | —      | —                  | V      | VPKI = 5 V, IF2F = -0.5 mA                              |

| Positive<br>threshold<br>voltage     | LDI                   | VTH+4           | 6           | 2.5                | —      | 3.5                | V      |                                                         |

|                                  |                                     |                  |             |      | (Ta =  | -20 to 75 | 5°C, V <sub>CC</sub> = | 5 V, unless otherwise noted)                                                                                                                |

|----------------------------------|-------------------------------------|------------------|-------------|------|--------|-----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                     |                  | Test        |      | Limits |           |                        |                                                                                                                                             |

| Item                             |                                     | Symbol           | Circ<br>uit | Min  | Тур    | Мах       | Unit                   | Test Conditions                                                                                                                             |

| Negative<br>threshold<br>voltage | LDI                                 | VTH-4            | 6           | 1.5  | —      | 2.7       | V                      |                                                                                                                                             |

| Hysterisis<br>width              | LDI                                 | VHY4             | _           | 0.5  | —      | 1.5       | V                      | (VTH+4) – (VTH–4)                                                                                                                           |

| Standby<br>circuit current       | V <sub>CC1</sub> , V <sub>CC2</sub> | ICCW             | 1           |      | 0.7    | 1.0       | mA                     | $V_{IN} = 0 mVp-p$                                                                                                                          |

| Operating<br>circuit current     | V <sub>CC1</sub> , V <sub>CC2</sub> | ICCR             | 1           | _    | 1.9    | 2.4       | mA                     | $\label{eq:III} \begin{array}{l} f_{IN} = 8.2 \ \text{kHz} \\ V_{IN} = 68 \ \text{mVp-p sine wave} \\ f_{OSC} = 1 \ \text{MHz} \end{array}$ |

| Oscillation<br>frequency         | RCP                                 | f <sub>OSC</sub> | 1           | 0.75 | _      | 1.5       | MHz                    | C <sub>OSC</sub> = 33 pF                                                                                                                    |

| Output pulse<br>width            | RCP                                 | TOW              | 7           | 15   | 16     | 17        | μs                     | f <sub>OSC</sub> = 1 MHz                                                                                                                    |

| Intra-output<br>delay time       | RDT, RCP                            | TOD              | 7           | 7    | 8      | 9         | μs                     | f <sub>OSC</sub> = 1 MHz                                                                                                                    |

| Input noise<br>width             | INV                                 | TNW              | 7           | 0.5  | _      | _         | μs                     |                                                                                                                                             |

Note: 1. Min. and max. limits do not represent absolute values.

2. Typ. limits represent standard values when Ta =  $25^{\circ}C$  and V<sub>CC</sub> = 5V.

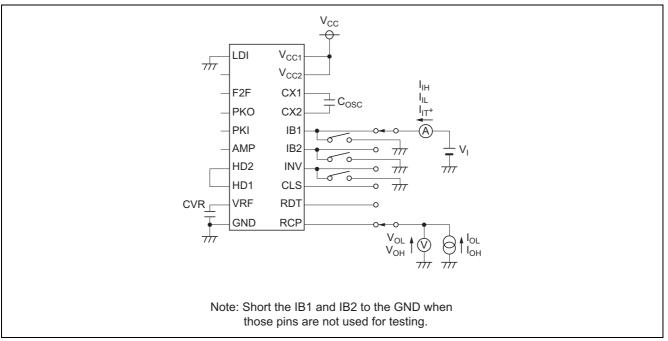

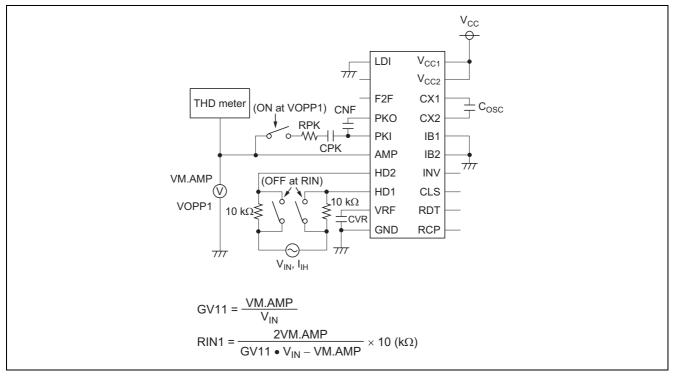

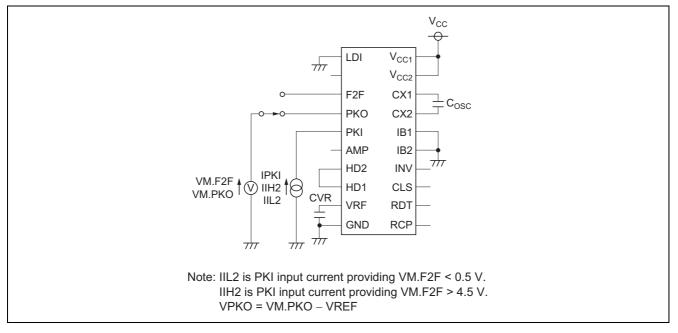

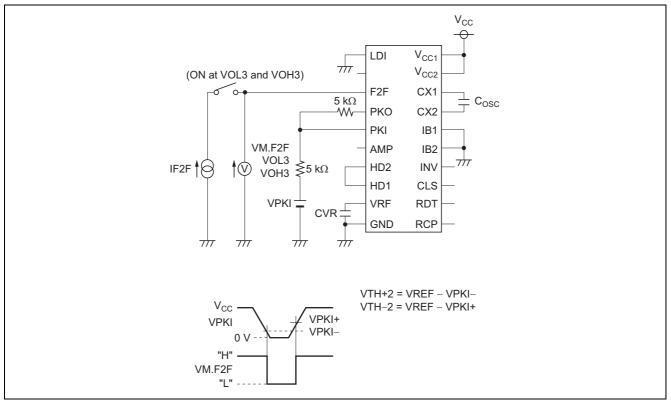

# **Test Circuit**

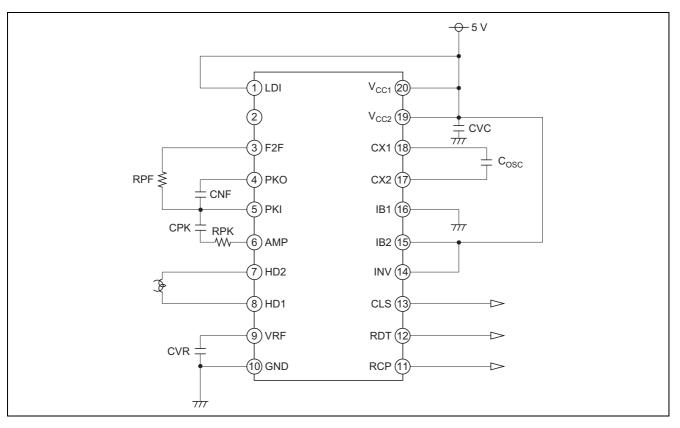

On the following drawing,  $C_{OSC} = 33 \text{ pF}$ , RPK = 470  $\Omega$ , CPK = 0.033  $\mu$ F, CNF = 470 pF, CVR = 1  $\mu$ F

1. Testing of VREF, ICCW, ICCR, fosc

2. Testing of  $V_{OL}$ ,  $V_{OH}$ ,  $I_{IL}$ ,  $I_{IH}$ ,  $I_{IT+}$

3. Testing of GV11, GV21, RIN1, VOPP1

### M56710FP

4. Testing of IIH2, IIL2, VPKO

5. Testing of VTH+2, VTH-2, VOL3, VOH3

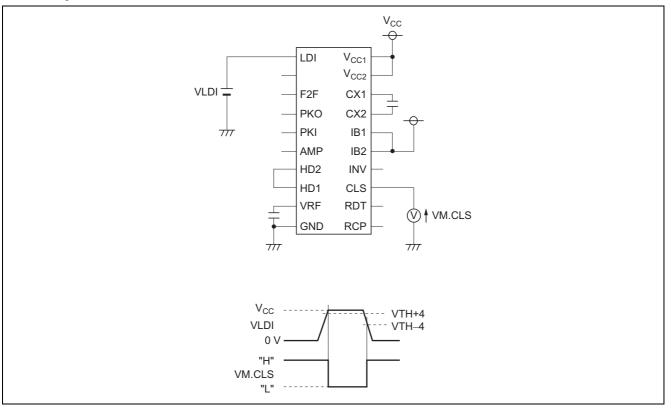

6. Testing of VTH+4, VTH-4

## 7. Testing of TOW, TOD, TNW

# **Application Example**

When setting the glance-over bit to 16 bits to let it be "L" active output

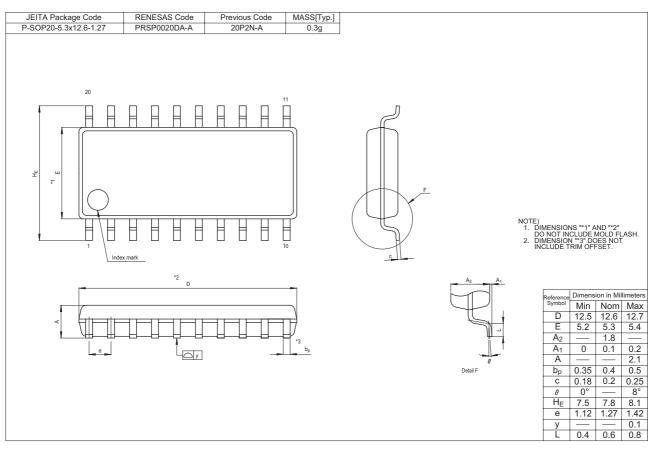

# **Package Dimensions**

# RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the date this document, when exporting the products or the technology described herein, you should follow the applicable export control laws and regulations, and proceedures required by such laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a fast stude of the document. You should evaluate the information in light of the total system before deciding about the applicability or there were provided specific by series as subal table. The subality of the series of the subality of the series of the subality of the series as subality of the series of any damages incurred as a state of the date this document.

When using or otherwise regulations in the information in this document. Dut Renesas as subality of that series of any damages incurred as a state of otherwise systems for transportation and traffic by the series of the series of the series of the series of the

### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

## Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com