rfmd.com

# RF6652 POWER MANAGEMENT IC

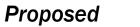

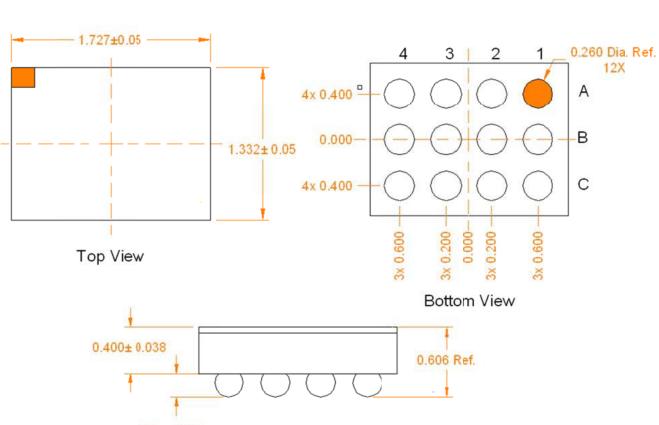

#### Package: 12-Bump WLSCP, 4 x 3 Array 1.65mm x 1.25mm

# **Features**

- Digital Mode Control Compatibility

- Provides the PA biasing for Three Power Modes (HP, MP, LP)

- Optimum Performance with RFMD's High Efficiency PA products

- Interface to Multiple PA(s)

- Optimized Maximum V<sub>CC</sub> at 3.4V

- High Efficiency >94%

- Transient Response <25µs</li>

- 650mA Load Current Capability

- V<sub>BAT</sub> Range = 2.7V to 5.0V

- Automatic Bypass Mode

- Over-Temperature Shutdown

- Over-Current Shutdown

## Applications

- WCDMA Handsets

- CDMA Handsets

- UMTS Datacards

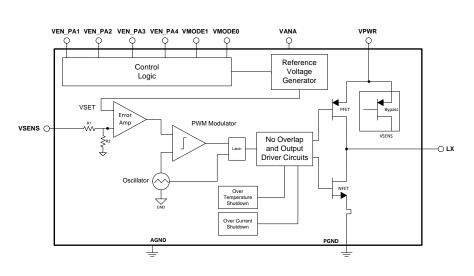

Functional Block Diagram

## **Product Description**

Proposed

The RF6652 is a pulse width modulated (PWM), discrete voltage-mode controlled DC-DC converter unit designed to supply power to a WCDMA power amplifier. The output voltage can be programmed by two control logic inputs to select the power mode for the PA. The DC-DC converter has been optimized for high efficiency at light current load conditions when PA is in low power mode. The RF6652 DC-DC PMIC offers fast transient response times to meet WCDMA 25µs slot-to-slot transition specifications and low noise by maintaining a constant switching frequency while supplying up to 650mA in PWM mode. The RF6652 is enabled when the PA enables ( $V_{EN} > 1.3V$ ) and  $V_{MODE0}$  and  $V_{MODE1}$  are used to select the  $V_{CC}$  to be supplied to the PA for each power mode. The RF6652 is a 1.65mm x 1.25mm, 12-bump, WLSCP device.

#### **Ordering Information**

RF6652Power Management ICRF665299PCBA-410Fully Assembled Evaluation Board

#### **Optimum Technology Matching® Applied**

| 🗌 GaAs HBT  | SiGe BiCMOS | ☐ GaAs pHEMT | 🗌 GaN HEMT |

|-------------|-------------|--------------|------------|

| GaAs MESFET | Si BiCMOS   | 🗹 Si CMOS    | BIFET HBT  |

| InGaP HBT   | SiGe HBT    | 🗌 Si BJT     |            |

RF MICRO DEVICES®, RRMD®, Optimum Technology Matching®, Enabling Wireless Connectivity<sup>10</sup>, PowerStard®, PoulARIS<sup>104</sup> TOTAL, RADIO<sup>104</sup> and UtimateBlue<sup>104</sup> are trademarks of RFMD, LLC, BLUETOOTH is a trade mark noved by Builenoth Sili, co. ILS A and Utimate of the TBMD, All other trade names is referenced and enables of trademarks and redistered trademarks. The trademarks and redistered trademarks and trademarks and redistered trademarks and trademar

7628 Thorndike Road, Greensboro, NC 27409-9421 · For sales or technical support, contact RFMD at (+1) 336-678-5570 or customerservice@rfmd.com.

# **RF6652**

# Proposed

rfmd.com

#### **Absolute Maximum Ratings**

| -                                                                                        |                               |      |  |  |  |

|------------------------------------------------------------------------------------------|-------------------------------|------|--|--|--|

| Parameter                                                                                | Rating                        | Unit |  |  |  |

| Input Supply Voltage                                                                     | -0.2 to +5.0                  | V    |  |  |  |

| Analog/Digital Inputs ( VEN_DC,<br>VMODEO, VMODE1, VEN_PA1,<br>VEN_PA2, VEN_PA3, VEN_PA4 | -0.2 to V <sub>ANA</sub> +0.2 | V    |  |  |  |

| Ground Voltage                                                                           | -0.2 to +0.2                  | V    |  |  |  |

| Operating Ambient Temperature                                                            | -30 to +85                    | °C   |  |  |  |

| Storage Temperature                                                                      | -55 to +150                   | °C   |  |  |  |

Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

RFMD Green: RoHS compliant per EU Directive 2002/95/EC, halogen free per IEC 61249-2-21, < 1000 ppm each of antimony trioxide in polymeric materials and red phosphorus as a flame retardant, and <2% antimony in solder.

| Devenator                         | Specification |                | Unit | Condition |                                                                                                                      |  |

|-----------------------------------|---------------|----------------|------|-----------|----------------------------------------------------------------------------------------------------------------------|--|

| Parameter                         | Min.          | Min. Typ. Max. |      | Unit      | Condition                                                                                                            |  |

| Operating Conditions              |               |                |      |           |                                                                                                                      |  |

| Supply Voltage                    | 2.7           | 3.6            | 5.0  | V         |                                                                                                                      |  |

| Output Load Current               |               |                | 650  | mA        |                                                                                                                      |  |

| Junction Temperature              | -30           |                | +125 | °C        |                                                                                                                      |  |

| Operating Temperature             | -30           |                | +85  | °C        |                                                                                                                      |  |

| General Specifications            |               |                |      |           |                                                                                                                      |  |

| Quiescent Current                 |               | 700            | 1400 | μΑ        | Internal V <sub>SET</sub> = 0V, no load                                                                              |  |

| Shut Down Current                 |               |                | 10   | μΑ        | $V_{\text{EN}_{PA1}} = V_{\text{EN}_{PA2}} = V_{\text{EN}_{PA3}} = V_{\text{EN}_{PA4}} = OV$                         |  |

| Logic High Input Threshold        | 1.3           |                |      | V         | V <sub>EN_DC</sub> , V <sub>MODE0</sub> , V <sub>MODE1</sub> , V <sub>EN_PA1</sub> , V <sub>EN_PA2</sub> ,           |  |

| Logic Low Input Threshold         |               |                | 0.5  | V         | V <sub>EN_PA3</sub> , V <sub>EN_PA4</sub>                                                                            |  |

| Input Current                     |               |                | 1.0  | μA        | Max current on any logic pin                                                                                         |  |

| Thermal Shutdown                  |               | 150            |      | °C        | Rising Temperature                                                                                                   |  |

|                                   |               | 130            |      | °C        | Falling Temperature                                                                                                  |  |

|                                   |               | 20             |      | °C        | Hysteresis                                                                                                           |  |

| Over-Current Shutdown Trip Points |               | 2.4            |      | A         | Full FET, V <sub>OUT</sub> = 3.4V                                                                                    |  |

|                                   |               | 1.6            |      | A         | 1/3 FET, V <sub>OUT</sub> = 0.8V                                                                                     |  |

| DC Specifications                 |               |                |      |           |                                                                                                                      |  |

| V <sub>OUT</sub>                  |               | 3.40           |      | V         | V <sub>MODEO</sub> = 0, V <sub>MODE1</sub> = 0                                                                       |  |

|                                   |               | 1.06           |      | V         | V <sub>MODE0</sub> = 1, V <sub>MODE1</sub> = 0                                                                       |  |

|                                   |               | 0.65           |      | V         | V <sub>MODEO</sub> = 1, V <sub>MODE1</sub> = 1                                                                       |  |

| V <sub>OUT</sub> Error            |               |                | 2.0  | %         | All modes, V <sub>BAT</sub> = 3.4V to 4.8V                                                                           |  |

| Efficiency                        |               | 66             |      | %         | V <sub>OUT</sub> = 0.8V, I <sub>OUT</sub> = 20mA                                                                     |  |

|                                   |               | 85             |      | %         | V <sub>OUT</sub> = 0.8V, I <sub>OUT</sub> = 60mA                                                                     |  |

|                                   |               | 92             |      | %         | V <sub>OUT</sub> = 1.40V, I <sub>OUT</sub> = 200mA                                                                   |  |

|                                   |               | 94             |      | %         | V <sub>OUT</sub> = 3.4V, I <sub>OUT</sub> = 550mA                                                                    |  |

| Output Voltage Ripple             |               | 15             |      | mVpp      | MPM, V <sub>OUT</sub> = 1.49V                                                                                        |  |

| Dropout Voltage                   |               | 170            |      | mV        | HPM, $V_{BAT}$ = 3.4V, $I_{OUT}$ = 500mA , (R <sub>ESRL</sub> = 100m $\Omega$ ),<br>$V_{DO}$ = $V_{BAT}$ - $V_{OUT}$ |  |

| Load Regulation                   |               |                | 20   | mV/A      | Low Power Mode, $V_{OUT} = 0.8V$ , $I_{OUT} = 20$ mA to 60mA                                                         |  |

|                                   |               |                | 20   | mV/A      | Medium Power Mode, V <sub>OUT</sub> = 1.49V, I <sub>OUT</sub> = 60mA to 200mA                                        |  |

|                                   |               |                | 20   | mV/A      | High Power Mode, V <sub>OUT</sub> = 3.4 V, I <sub>OUT</sub> = 400mA to 550mA                                         |  |

RF6652

| Paramatar                              | Specification |      | Unit | Condition |                                                                                                                                |

|----------------------------------------|---------------|------|------|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| Parameter                              | Min.          | Тур. | Max. | Unit      | Condition                                                                                                                      |

| DC Specifications (continued)          |               |      |      |           |                                                                                                                                |

| Line Regulation                        |               |      | 10   | mV/A      | Low Power Mode, $V_{OUT}$ = 0.8V, $I_{OUT}$ = 25mA, $V_{BAT}$ = 3.3V to 3.9V                                                   |

|                                        |               |      | 10   | mV/A      | Medium Power Mode, $V_{OUT}$ = 1.49V, $I_{OUT}$ = 60mA, $V_{BAT}$ = 3.3V to 3.9V                                               |

|                                        |               |      | 10   | mV/A      | High Power Mode, $V_{OUT}$ = 3.4V, $I_{OUT}$ = 450mA,<br>V <sub>BAT</sub> = 3.6V to 4.2V                                       |

| AC Specifications                      |               |      |      |           |                                                                                                                                |

| Switching Frequency                    |               | 2    |      | MHz       | Over V <sub>BAT</sub> and temperature                                                                                          |

| V <sub>OUT</sub> Startup Time          |               | 12   | 35   | μS        | $V_{OUT}$ = 0V to 0.6V ±10%, $I_{OUT}$ < 1mA                                                                                   |

|                                        |               | 6    | 35   | μS        | $V_{OUT}$ = 0V to 3.4V ±10%, $I_{OUT}$ < 1mA, $V_{BAT} \ge$ 4.2V                                                               |

| V <sub>OUT</sub> Response Time         |               | 8    | 25   | μS        | $V_{OUT}$ = 0.6V to 3.4V ±100mV, R <sub>LOAD</sub> = 5Ω, V <sub>BAT</sub><br>≥ 4.2V                                            |

|                                        |               | 9    | 30   | μS        | $V_{OUT} = 3.4V \text{ to } 0.6V \pm 100 \text{mV}, \ \text{R}_{\text{LOAD}} = 25 \Omega, \\ V_{\text{BAT}} \geq 4.2 \text{V}$ |

| SMPS to BYPASS Time                    |               | 1.5  | 5    | μS        | MPM to HPM, $I_{OUT}$ = 460 mA, $V_{BAT}$ = 3.0V                                                                               |

|                                        |               | 4    | 20   | μS        | V <sub>BAT</sub> = 4.6V to 3.0V, I <sub>OUT</sub> = 460mA, HPM                                                                 |

| BYPASS to SMPS Time                    |               | 40   | 50   | μS        | HPM to MPM, $I_{OUT}$ = 460mA, $V_{BAT}$ = 3.0V                                                                                |

|                                        |               | 10   | 50   | μS        | $V_{BAT}$ = 3.0V to 4.6V, $I_{OUT}$ = 460 mA, HPM                                                                              |

| Load Transient                         |               | 30   | 100  | mVpk      | $V_{OUT}$ = 600mV, $I_{OUT}$ = 20mA to 200mA, $T_{RISE}$ = $T_{FALL}$ = 10 $\mu s$                                             |

|                                        |               | 16   | 50   | mVpk      | $V_{OUT}$ = 3.4V, $I_{OUT}$ = 400mA to 550mA, $V_{BAT}$ = 4.2V                                                                 |

| Line Transient                         |               | 30   | 35   | mVpk      | $V_{OUT}$ = 600mV, $I_{OUT}$ = 60mA, $\Delta V_{BAT}$ = 600mV,<br>$T_{RISE}$ = $T_{FALL}$ = 10 $\mu$ s                         |

|                                        |               | 135  | 150  | mVpk      | $V_{OUT} = 3.4V$ , $I_{OUT} = 450$ mA, $\Delta V_{BAT} = 600$ mV,<br>$T_{RISE} = T_{FALL} = 10$ µs, $V_{BAT} = 4.2V$           |

| Bypass Specifications                  |               |      |      |           |                                                                                                                                |

| Resistance                             |               | 140  | 200  | mΩ        | V <sub>BAT</sub> = 3.0V, I <sub>OUT</sub> = 500mA (net resistance)                                                             |

| Enable Trip Point (V <sub>BAT</sub> )  |               | 3.5  |      | V         | Falling V <sub>BAT</sub> , I <sub>OUT</sub> = 500mA, HPM                                                                       |

| Disable Trip Point (V <sub>BAT</sub> ) |               | 3.7  |      | V         | Raising V <sub>BAT</sub> , I <sub>OUT</sub> = 500mA, HPM                                                                       |

| Dropout Voltage                        |               |      | 100  | mV        | $V_{BAT}$ = 3.0V, $I_{OUT}$ = 500mA, Dropout = $V_{BAT}$ - $V_{OUT}$                                                           |

| V <sub>OUT</sub> Startup Time          |               | 4    | 15   | μS        | $V_{BAT}$ = 3.0V. $I_{OUT} \le 1$ mA                                                                                           |

# V<sub>OUT</sub> Values for all Four VEN\_PAx Selections

(These Values are Factory Set for the RF6652)

| V <sub>OUT</sub> Values for each Mode | VEN_PA1 | VEN_PA2 | VEN_PA3 | VEN_PA4 |  |  |  |

|---------------------------------------|---------|---------|---------|---------|--|--|--|

| High Power Mode                       | 3.4V    | 3.4V    | 3.4V    | 3.4V    |  |  |  |

| Medium Power Mode                     | 1.48V   | 1.48V   | 1.36V   | 1.36V   |  |  |  |

| Low Power Mode                        | 0.84V   | 0.84V   | 0.78V   | 0.76V   |  |  |  |

# RF6652

rfmd.com

# **Pin Names and Descriptions**

| Pin | Name    | Description                                                                                                                                                                                  |  |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1  | PGND    | DC-DC Converter Power Ground                                                                                                                                                                 |  |

| A2  | LX      | DC-DC Converter Switcher Output. Connect to the filter inductor as recommended on application sche-<br>matics. Provides three set voltages to correspond to HP, MP, and LP modes for the PA. |  |

| A3  | VPWR    | Supply used for the DC-DC PFET switch. A 2.2 $\mu\text{F}$ decoupling capacitor is required on this pin                                                                                      |  |

| A4  | VSNS    | Feedback node from the output of the external LC filter. Connect at a point after the VOUT inductor and/or near the PA VCC pin.                                                              |  |

| B1  | VEN_PA2 | Logic level that selects a specific internal PA biasing levels for LP, MP, and HP modes.                                                                                                     |  |

| B2  | VEN_PA1 | Logic level that selects a specific internal PA biasing levels for LP, MP, and HP modes.                                                                                                     |  |

| B3  | VMODE0  | DEO Logic level that selects the power mode (HP, MP, or LP mode)                                                                                                                             |  |

| B4  | VMODE1  | Logic level that selects the power mode (HP, MP, or LP mode)                                                                                                                                 |  |

| C1  | AGND    | Ground for the analog circuits. Isolate from the PGND to better reduce noise.                                                                                                                |  |

| C2  | VEN_PA4 | Logic level that selects a specific internal PA biasing levels for LP, MP, and HP modes.                                                                                                     |  |

| C3  | VEN_PA3 | Logic level that selects a specific internal PA biasing levels for LP, MP, and HP modes.                                                                                                     |  |

| C4  | VANA    | Supply used for the analog circuitry inside the RF6652 power management IC. A 2.2 $\mu F$ decoupling capacitor is required.                                                                  |  |

# **Pin Out** QB Single-Ended (Bottom View)

Note: VEN\_PA4 will be treated as VEN\_DC in the configuration with three (3) PAs and a seperate DC-DC Enable.

# **Theory of Operation**

DC-DC buck converter operation involves the stepping down of a higher battery voltage to a lower output voltage by alternately switching a PFET and NFET pair through an external LC filter. At a 2MHz switching frequency the PFET is enabled every 500ns. Based on the power mode of the PA, an accurate internal reference voltage  $V_{SET}$  is set up. The duty cycle at the Lx switching node, which is continuously variable from 0% to 100%, is set by the PWM controller based on internal  $V_{SET}$  and  $V_{BAT}$  voltages to realize the desired output voltage. The PWM controller maintains accuracy, stability, and accounts for losses in the system by feedback through the VSENS pin. The controller has been designed with non-overlapping control circuitry to prevent  $V_{BAT}$  overshoot-through current to ground.

The converter has been optimized for high efficiency at light load by balancing DC and AC switching losses incurred in the output FETs, the switching frequency, and the external LC filter. In addition, output FET segmentation and selective biasing have been employed to further enhance light load efficiencies.

Unlike other DC-DC converter solutions on the market, the RF6652 does not alter the switching frequency at light load conditions to boost efficiency. This type of efficiency enhancement has a severe detriment on the system by injecting spurious noise at various frequencies. With our expertise in front end transmit module design, RFMD proposes to operate this converter at a constant switching frequency to minimize system level interference. The ripple voltage, also a major component of noise injection into the PA, has also been minimized by selecting a larger inductance value.

Despite the attention to high efficiency, the transient performance of the device, defined as an output voltage transient from 600mV to 3.4V or vice-versa, has not been overlooked. The PWM controller has been properly tuned with a fast type III loop filter to mate with an external LC filter (L =  $2.2\mu$ H and C =  $2.2\mu$ F +  $1\mu$ F +  $1\mu$ F =  $4.2\mu$ F). The result is a converter with sufficient bandwidth to meet  $25\mu$ s WCDMA slot-to-slot transition time requirements.

(Note: If four PA(s) are used then a  $0.47\mu$ F can be placed at each of the four PA VCC pins. If only two PA(s) are used, then a  $1\mu$ F can be at both PA VCC pins.

Lastly, the external inductor and capacitors were specifically selected to balance efficiency over the load current operating range and transient performance while minimizing total board area. Inductors and capacitors of different values may be used at risk to DC-DC converter stability and efficiency performance.

#### **Control Interface**

The  $V_{MODE0}$  and  $V_{MODE1}$  will adjust what power mode the PA will be in and load condition of the RF6652.

| VMODEO | VMODE1 | PA Mode      |  |  |  |  |

|--------|--------|--------------|--|--|--|--|

| 0      | 0      | High Power   |  |  |  |  |

| 1      | 0      | Medium Power |  |  |  |  |

| 1      | 1      | Low Power    |  |  |  |  |

## Input Logic Table to provide PA power mode control

#### Shutdown

The shutdown mode is determined by the following logic table:

| VEN_PA1                    | VEN_PA2 | VEN_PA3 | VEN_PA4 | VMODE1 | VMODE0 |  |

|----------------------------|---------|---------|---------|--------|--------|--|

| 0                          | 0       | 0       | 0       | Х      | Х      |  |

| X = "Don't Care" Condition |         |         |         |        |        |  |

Proposed

#### **Over-Temperature Protection**

An internal over-temperature shutdown circuit is employed to protect the device from excessively high junction temperatures. The shutdown occurs at typically 150°C and will re-enable when the temperature drops below the activation point typically by 20°C.

#### **Over-Current Protection**

For the RF6652, an over-current shutdown (OCSD) circuit is employed to provide over-current fault protection. This methodology deactivates the output FETs in the case of an over-current fault as opposed to limiting the current. In this way the device only experiences the over-current condition for a short transient period and is not subject to continuous high current flow. Once the DUT is shut down, it will not restart automatically if the fault condition is removed.

#### **Bypass Mode**

RF6652 contains an automatic bypass mode that activates a large PFET device in parallel with the SMPS PFET when there is insufficient headroom available between  $V_{BAT}$  and the desired output voltage. This mode is enabled when there is less than 100mV of headroom available and is disabled when the available headroom increases above 300mV. The bypass FET reduces the output resistance and dropout voltage at high power mode.

#### **FET Segmentation**

The main power FETs are designed in three sections to improve efficiency during light load conditions expected with low output voltages. In medium and high power modes, all three sections of the output FETs are on (full FET mode). When the part operates in low power mode, only one of the three sections is used (1/3 FET mode).

#### **Board Layout**

Good DC-DC converter layout practices in this application are strongly recommended to reduce radiated and conducted system noise. Placement of the VPWR bypass capacitor is critical and must be such to minimize the AC supply and ground return current loop through the PFET. In addition, the placements of the LC filter (L1 and C1) are also critical to minimize the AC supply and ground return current loop through the NFET.

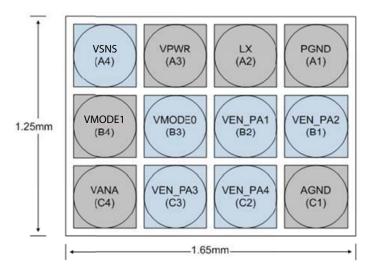

# **Application Schematic**

Notes: RF6652 and PA Application with related EVB components:

- 1. The LC filter (power filter) consists of L1 and C1 near the RF6652 and the distributed capacitances C6 thru C9 near load (PA)s. The main loop of L1 and C1 should be as small as possible with a large ground plane connecting C1 to the PGND pin. Capacitors C6, C7, C8, C9 are placed at the VCC pins of the loads (each PA V<sub>CC</sub>) and should also have a clear return path to PGND. The loop filter is designed to have a total capacitance of  $4.2\mu$ F (C1 =  $2.2\mu$ F +  $1\mu$ F +  $1\mu$ F) or equal to (C1 =  $2.2\mu$ F +  $4 \times (0.47\mu$ F). This would be the configuration for four PA(s).

- 2. Capacitors C2 and C3 are placed a small distance away from the DUT on the evaluation board to emulate the distributed effects of the trace resistance as would be expected in the application.

- 3. A separate decoupling capacitor should be used for the VPWR and VANA pins. The current return path for the analog and power sections should be kept separate to decrease the number of component types, a value of 2.2μF is selected.

- 4. The parasitic resistance of L1 and C1 should be kept within the limits RESRL<100mΩ, R<sub>ESRC</sub> = 10mΩ. Recommended components are given in the table below. Selecting alternate components will have an impact on the reported performance including, but not limited to, changes in the efficiency.

| Decignator | Designator Case Size Ouantity Manufacturer Value Part Number |          |              |             |                    |  |

|------------|--------------------------------------------------------------|----------|--------------|-------------|--------------------|--|

| Designator | Case Size                                                    | Quantity | Manufacturer | value       | Part Number        |  |

| L1         | 2.5 X 2.0 X 1.0                                              | 1        | 2.2μH        | Murata      | LQM2HPN2R2MGOL     |  |

| C1         | 0603                                                         | 1        | 2.2μF        | Murata      | GRM188R61A225KE34D |  |

| C2, C3     | 0603                                                         | 2        | 1μF          | Taiyo Yuden | RMTMK107BJ105KA-T  |  |

## **Application Schematic and Related EVB Components**

# Proposed

rfmd.com

**Package Drawing**