Communication Solutions

# E-GOLDvoice GSM Voice Only Single Chip Solution CONFIDENTIAL

**Revision History: 2006-12-06, Rev. 1.05**

| Previous \ | Previous Version: 2006-10-04, Rev. 1.04                                                                                                             |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Page       | Subjects (major changes since last revision)                                                                                                        |  |

| All Pages  | Design Specification updates for Power Domains names & Electrical Characteristics (SMS00147105, SMS00429563, SMS00417279)                           |  |

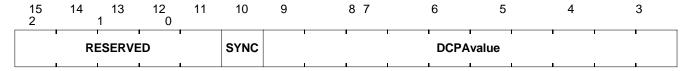

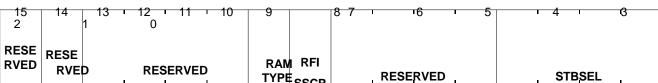

|            | Design Specification updates for RF macro (SMS00330373, SMS00254415, SMS00429579, SMS00323765)                                                      |  |

|            | Design Specification updates for LDO (SMS00366822, SMS00414335, SMS00414336, SMS00415798)                                                           |  |

|            | Design Specification updates for PMU macro (SMS00414331, SMS00418894, SMS00420316, SMS00425149, SMS00429427, SMS00429435, SMS00429437, SMS00425315) |  |

|            | Design Specification updates for BootCode Utility routines (SMS00415783)                                                                            |  |

|            | Design Specification updates for E-Fuse Boxes (SMS00424075)                                                                                         |  |

| All Pages  | Update Product Versions / RePrint of Book                                                                                                           |  |

|            |                                                                                                                                                     |  |

#### **Trademarks**

ABM®, ACE®, AOP®, Arcofi®, ASM®, ASP®, BlueMoon®, BlueNIX®, C166®, DUALFALC®, DuSLIC®, ELIC®, EPIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, Ipat®-2, IPVD®, Isac®, ITAC®, IWE®, IWORX®, M-GOLD®, MUSAC®, MuSLIC®, OCTALFALC®, OCTAT®, POTSWIRE®, QUADFALC®, QUAT®, SCOUT®, SCT®, SEROCCO®, S-GOLD®, SICAT®, SICOFI®, SIDEC®, SIEGET®, SLICOFI®, SMARTI®, SOCRATES®, VDSLite®, VINETIC®, 10BaseS® are registered trademarks of Infineon Technologies AG.

ConverGate<sup>™</sup>, DIGITAPE<sup>™</sup>, EasyPort<sup>™</sup>, S-GOLDlite<sup>™</sup>, S-GOLD2<sup>™</sup>, S-GOLD3<sup>™</sup>, VINAX<sup>™</sup>, WildPass<sup>™</sup>, 10BaseV<sup>™</sup>, 10BaseV<sup>™</sup> are trademarks of Infineon Technologies AG.

Microsoft® and Visio® are registered trademarks of Microsoft Corporation. Linux® is a registered trademark of Linus Torvalds. FrameMaker® is a registered trademark of Adobe Systems Incorporated. APOXI® is a registered trademark of Comneon GmbH & Co. OHG. PrimeCell®, RealView®, ARM® are registered trademarks of ARM Limited. OakDSPCore®, TeakLite® DSP Core, OCEM® are registered trademarks of ParthusCeva Inc. IndoorGPS™, GL-20000™, GL-LN-22™ are trademarks of Global Locate. ARM926EJ-S™, ADS™, Multi-ICE™ are trademarks of ARM Limited.

## **Table of Contents**

|             | List of Figures                     | 10   |

|-------------|-------------------------------------|------|

|             | List of Tables                      | 15   |

| 1           | Introduction                        | 20   |

| 1.1         | Overview of E-GOLDvoice             | 20   |

| 1.2         | Features                            | 22   |

| 1.3         | Application                         | 23   |

| 1.4         | GSM System Description              |      |

| 1.5         | PMU Details                         |      |

| 1.6         | Bus Concept                         | 24   |

| 1.6.1       | C166S Buses                         | 24   |

| 1.6.2       | TEAKLite Bus                        | 24   |

| 1.6.3       | Bus Interconnections                | 25   |

| 1.7         | Clock Concept                       |      |

| 1.8         | Interrupt Concept                   |      |

| 1.9         | Debug Concept                       |      |

| 1.9.1       | C166 Debug Concept                  |      |

| 1.9.2       | TEAKLite Debug Concept              |      |

| 1.10        | Power Management                    | 25   |

| 1.11        | On-Chip Security Concept            |      |

| 1.12        | Asynchronous Operation Mode Concept | . 26 |

| 1.13        | Product Versions & Namings          |      |

| 1.14        | Package                             | 27   |

| 2           | Pin Diagram                         |      |

| <b>2</b> .1 | E-GOLDvoice Ballout                 |      |

| 3           | Pin Descriptions                    | 31   |

| 4           | Bus Overview                        | 38   |

| 5           | Digital and Mixed-Signal Subsystems | 39   |

| 5.1         | TEAKLite                            |      |

| 5.2         | C166S MCU                           |      |

| 5.3         | TEAKlite Bus                        |      |

| 5.3.1       | Interrupt Unit                      |      |

| 5.3.2       | Channel Decoder Accelerator         |      |

| 5.3.3       | I2S 1 (DAI)                         |      |

| 5.3.4       | Baseband Receiver                   |      |

| 5.3.5       | Voice                               | 41   |

| 5.3.6       | GSM Cipher Unit                     | 41   |

| 5.3.7       | Equalizer Accelerator               | 42   |

| 5.3.8       | Shared Memory                       | 42   |

| 5.3.9       | Program ROM                         |      |

| 5.3.10      | Program RAM                         | 42   |

| 5.3.11      | Data ROM                            |      |

| 5.3.12      | Data RAM                            |      |

| 5.3.13      | Multicore Synchronization           | . 42 |

| 5.3.14      | OCEM/SEIB                           |      |

| 5.4         | LM Bus                              | 44   |

| 5.4.1       | RAM                                 | 44   |

| 5.4.2            | ROM                                               | . 44 |

|------------------|---------------------------------------------------|------|

| 5.5              | X-Bus                                             | . 45 |

| 5.5.1            | Shared Memory                                     | 45   |

| 5.5.2            | Multicore Synchronization                         | . 45 |

| 5.5.3            | PLL - CGU - SCCU                                  | . 45 |

| 5.5.4            | Measurement                                       | 46   |

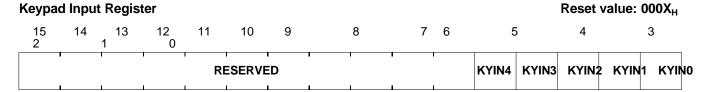

| 5.5.5            | Keypad                                            | 47   |

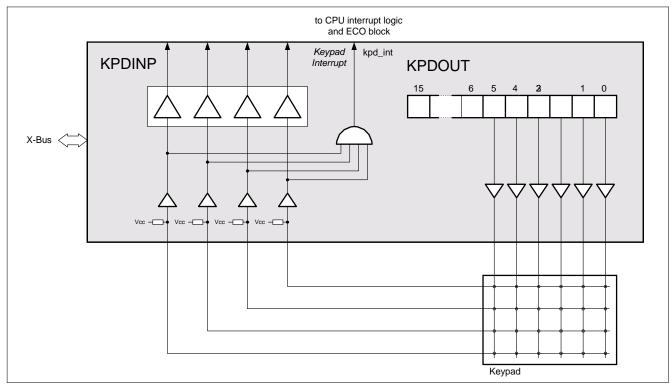

| 5.5.6            | SIM Interface                                     | 47   |

| 5.5.7            | RF Power Ramping                                  |      |

| 5.5.8            | GSM Timer                                         |      |

| 5.5.9            | EBU                                               |      |

| 5.6              | PD Bus                                            |      |

| 5.6.1            | I2C                                               |      |

| 5.6.2            | SSC                                               |      |

| 5.6.3            | ASC0                                              |      |

| 5.6.4            | CAPCOM1/2                                         |      |

| 5.6.5            | RTC                                               |      |

| 5.6.6            | GPT1/2                                            |      |

| 5.6.7            | Port Control Logic                                |      |

| 5.6.8            | TAP Controller & Boundary Scan and Break Switch   | . 51 |

| 6                | RF Subsystem                                      | . 52 |

| 6.1              | Pin Definition and Function                       | 52   |

| 6.1.1            | Receiver                                          | 53   |

| 6.1.2            | Transmitter                                       | 54   |

| 6.1.3            | RF-Synthesizer                                    | . 55 |

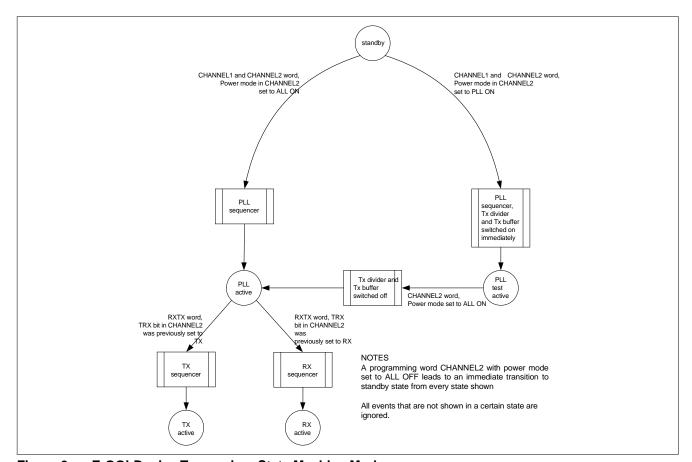

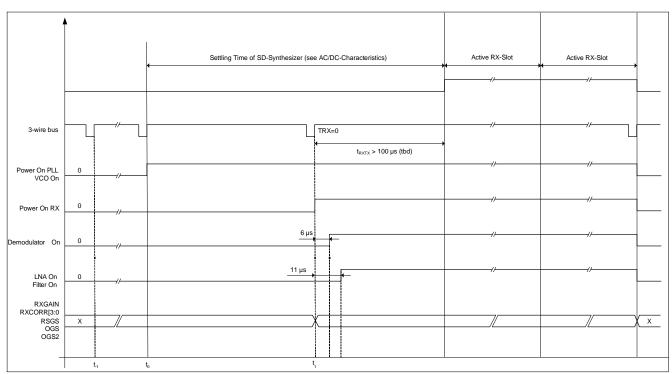

| 6.1.4            | Power Up Sequencer                                | 55   |

| 6.1.5            | 3-Wire Serial Bus                                 | 57   |

| 6.1.6            | DCXO                                              | . 58 |

| 7                | X-Bus                                             |      |

| 60               |                                                   |      |

| 7.1              | X-Bus Description                                 |      |

| 7.1.1            | X-Bus Interface                                   |      |

| 7.1.2            | 8- and 16-bit Access to X-Bus Peripherals         |      |

| 7.1.3            | Reset Behavior of X-Bus                           | -    |

| 7.2              | PLL - CGU - SCCU                                  |      |

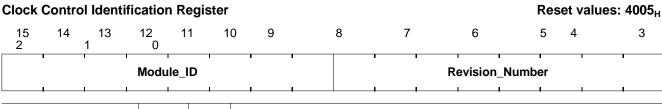

| 7.2.1            | Clock Generation Unit                             |      |

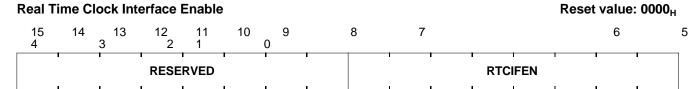

| 7.2.2            | Standby Clock Control Unit (SCCU)                 |      |

| 7.2.3            | Efuse Management                                  |      |

| 7.3              |                                                   | 113  |

| 7.3.1            | Functional Overview                               | 113  |

| 7.3.2            | Register Overview                                 | 114  |

| 7.3.3            | Measurement Circuit and Mode Setting              |      |

| 7.3.4            | Differential General Purpose Measurements (MxMy)  |      |

| 7.3.5            | Single-Ended General Purpose Measurements (Mx)    |      |

| 7.3.6            | On-Chip Temperature Measurement                   |      |

| 7.3.7            | Modulator Unit Offset Measurement TXOFI and TXOFQ |      |

| 7.3.8            | Offset Calibration of Measurement Interface       |      |

| 7.3.9            | 9 1                                               | 124  |

| 7.3.10<br>7.3.11 | Special Operating Modes and Examples              |      |

| 7.3.11           | Clock Control of Measurement Interface            |      |

| 1.3.12           | Ciden Control of Measurement interiace            | 130  |

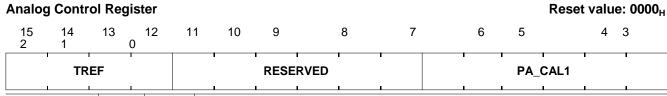

| 7.4          | Analog Control Registers                                      |       |

|--------------|---------------------------------------------------------------|-------|

| 7.4.1        | Functional Overview                                           |       |

| 7.4.2        | Analog Control Register 1                                     |       |

| 7.4.3        | Analog Control Register 2                                     |       |

| 7.5          | Keypad                                                        |       |

| 7.5.1        | Description                                                   |       |

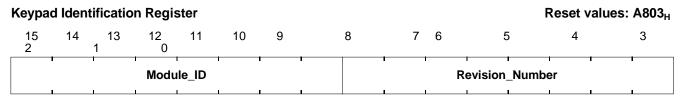

| 7.5.2        | Keypad Registers                                              |       |

| 7.5.3        | Keypad Port                                                   |       |

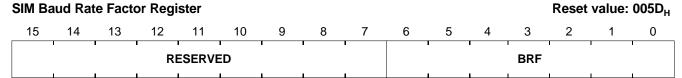

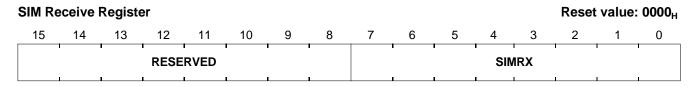

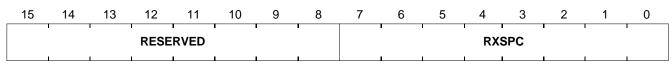

| 7.6          | SIM Interface                                                 |       |

| 7.6.1        | Functional Overview                                           |       |

| 7.6.2        | SIM Register Overview                                         |       |

| 7.6.3        | Register Description                                          |       |

| 7.6.4        | SIM Card Interface                                            |       |

| 7.6.5        | Clock Control                                                 |       |

| 7.6.6        | SIM Activation and Deactivation                               |       |

| 7.6.7        | Initialization Sequence Overview                              |       |

| 7.6.8        | Automatic Power Down                                          |       |

| 7.6.9        | SIM Character Mode                                            |       |

| 7.6.10       | SIM T=0 Protocol Mode                                         |       |

| 7.6.11       | Connection of 5 V, 3 V, and 1.8 V SIM Cards                   |       |

| 7.6.12       | SIM Card Pads                                                 |       |

| 7.7          | RF Power Ramping                                              |       |

| 7.7.1        | Introduction                                                  |       |

| 7.7.2        | Application Notes                                             |       |

| 7.7.3        | System Register                                               |       |

| 7.8          | RF Control                                                    |       |

| 7.8.1        | Introduction                                                  | 169   |

| 7.8.2        | RF RAM                                                        |       |

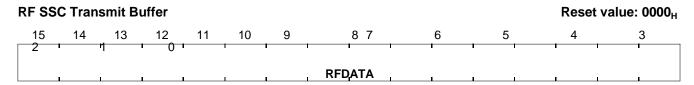

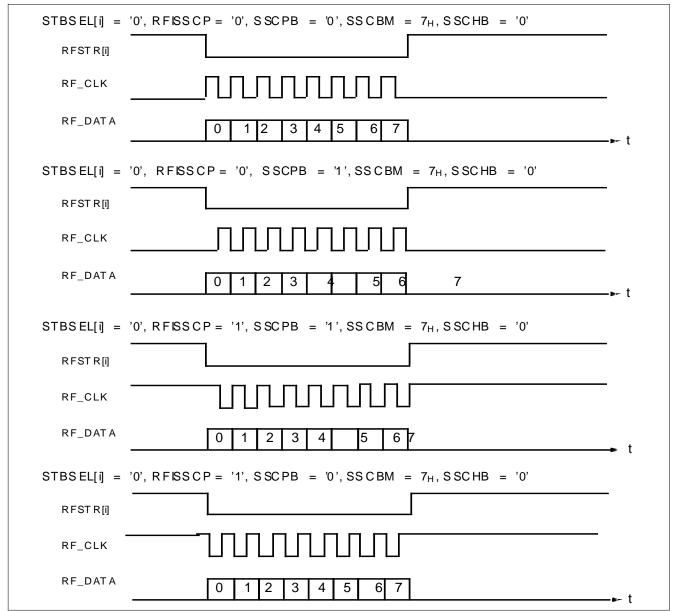

| 7.8.3        | Synchronous Serial Interface (3-wire RF interface)            | 174   |

| 7.8.4        | Control Block                                                 |       |

| 7.9          | GSM Timer Unit                                                |       |

| 7.9.1        | Overview                                                      | 181   |

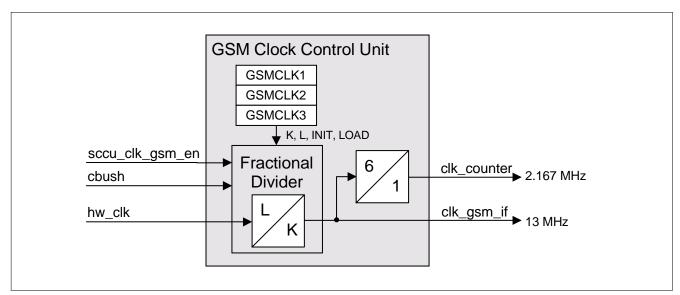

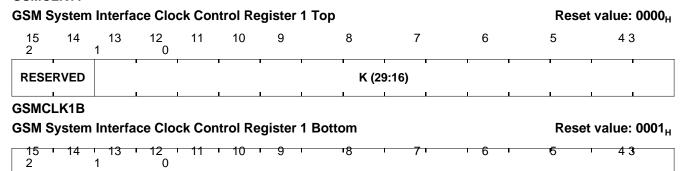

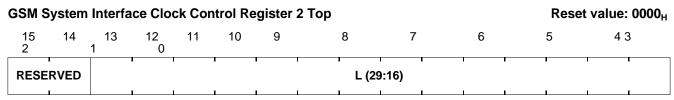

| 7.9.2        | GSM Clock Control Unit                                        | 196   |

| 7.9.3        | GSM Timer Decoder                                             | 200   |

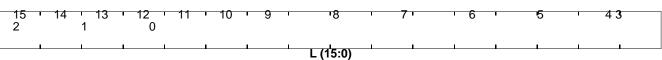

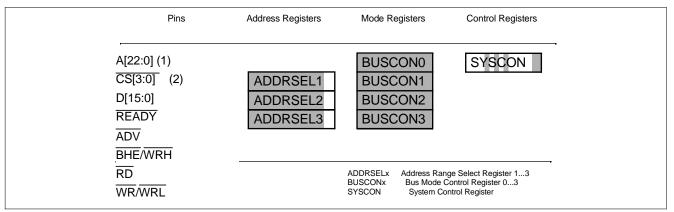

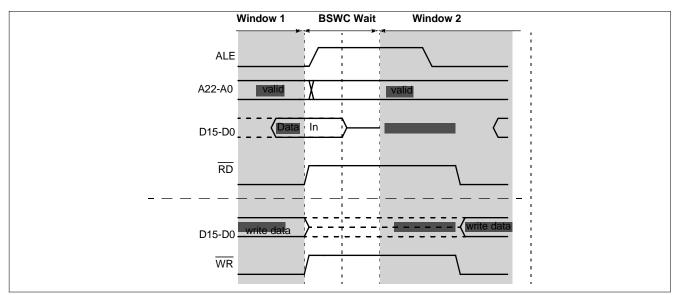

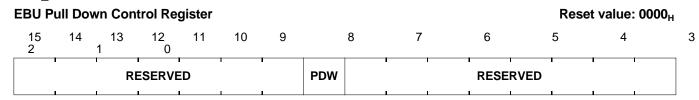

| 7.10         | External Bus Unit                                             | 202   |

| 7.10.1       | Introduction                                                  | 202   |

| 7.10.2       | Single-Chip Mode                                              | 202   |

| 7.10.3       | External Bus Modes                                            | 203   |

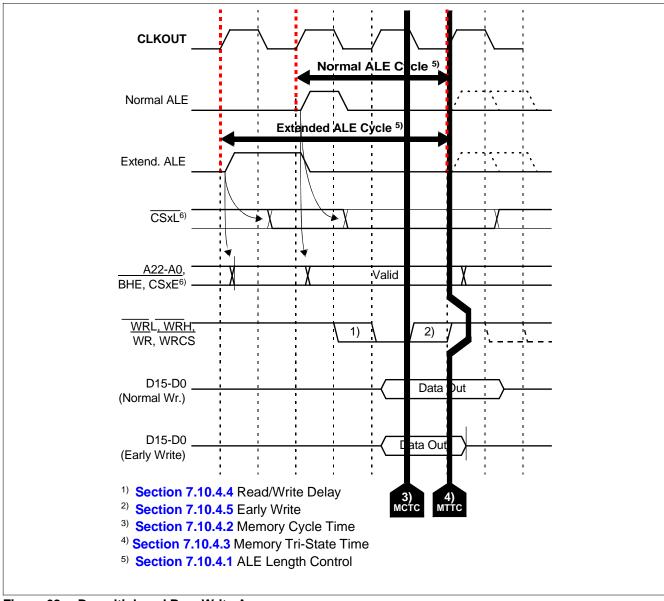

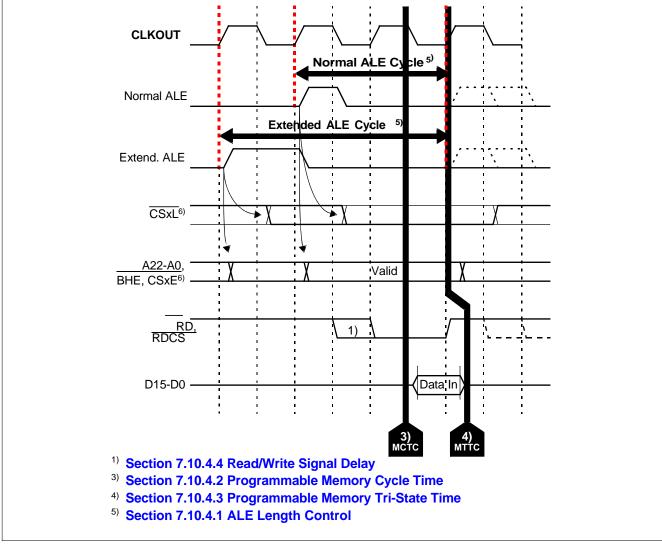

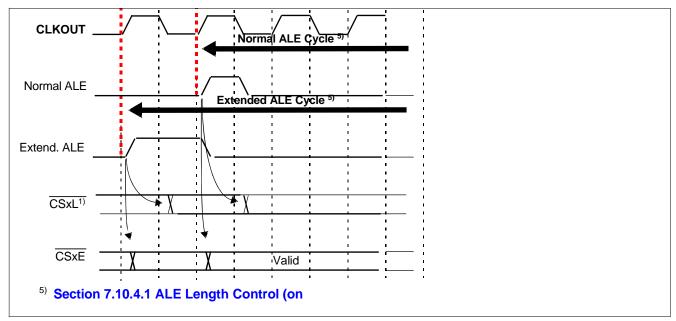

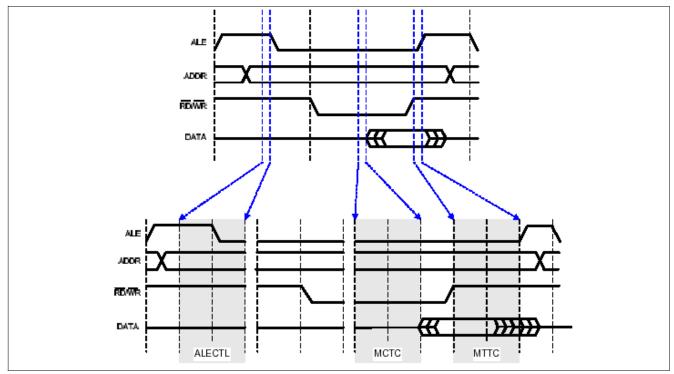

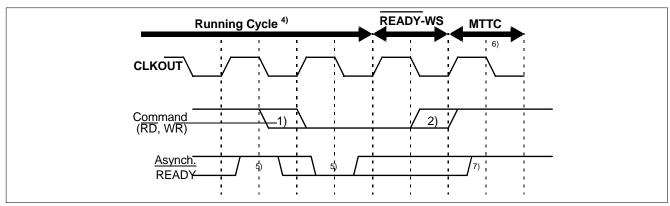

| 7.10.4       | Programmable Bus Characteristics                              | 210   |

| 7.10.5       | Controlling the External Bus Controller                       | . 214 |

| 7.10.6       | EBC Idle State                                                | 218   |

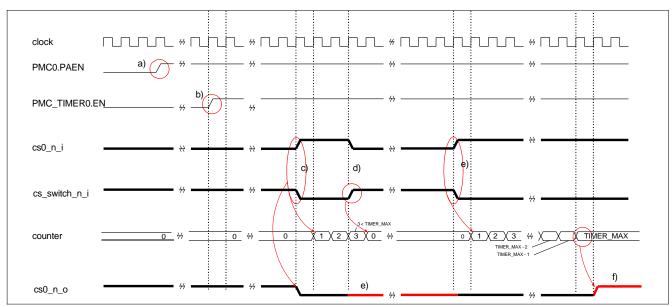

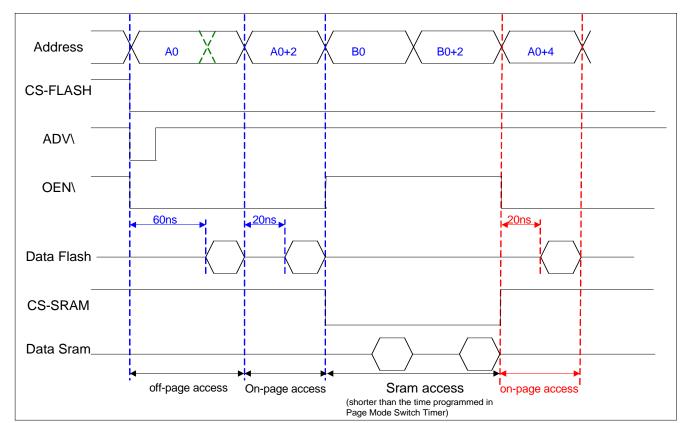

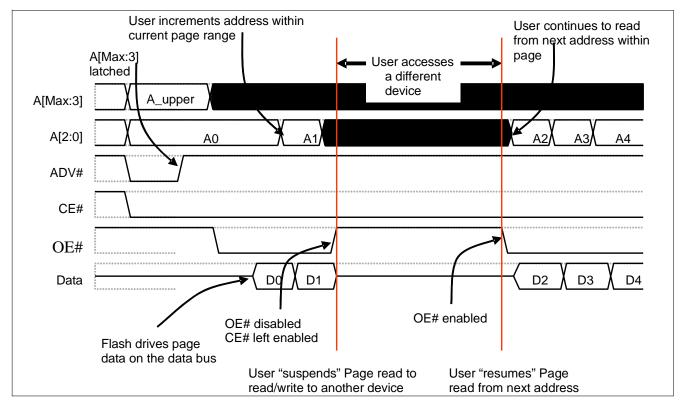

| 7.10.7       | Page Mode Flash Control Unit                                  | 219   |

| 8            | Power Management Unit                                         | . 233 |

| 8.1          | Features Overview                                             |       |

| 8.1.1        | PMU Register Overview                                         |       |

| 8.1.2        | System Power On/Off and Reset Control Logic                   |       |

| 8.1.3        | Linear Voltage Regulator LDO (Low DropOut)                    |       |

| 8.2          | Battery Charger                                               |       |

| o.∠<br>8.2.1 | Switched Charging                                             |       |

| 8.2.2        | Charger Detection                                             |       |

| 8.2.3        | Battery Over-Voltage Detection and Battery Voltage Monitoring |       |

| ∪.∠.∪        | Daliety Over vollage Delection and Daliety vollage Monthly    | 200   |

| 8.2.4 | Power ON Reset                           | 256 |

|-------|------------------------------------------|-----|

| 8.2.5 | IC Over-Voltage Protection               | 256 |

| 8.2.6 | Pre-Charging                             | 257 |

| 8.2.7 | Software Controlled Charging             | 257 |

| 8.2.8 | Thermal Design                           | 258 |

| 8.2.9 | Charge Current larger than 500 mA        | 258 |

| 8.3   | LED Current Generation                   | 259 |

| 8.3.1 | Digital Waveform Generation              | 259 |

| 8.3.2 | Mixed Analog/Digital Waveform Generation | 259 |

| 9     | PD-Bus                                   | 265 |

| 9.1   | I2C Bus Interface                        |     |

| 9.1.1 | Introduction                             |     |

| 9.1.2 | Operational Overview                     |     |

| 9.1.3 | Functional Overview                      |     |

| 9.1.4 | Registers                                |     |

| 9.1.5 | Reset Behavior                           |     |

| 9.1.6 | Interrupts                               |     |

| 9.1.7 | Synchronization                          |     |

| 9.1.8 | Programming                              |     |

| 9.2   | Synchronous Serial Interface             |     |

| 9.2.1 | Introduction                             |     |

| 9.2.2 | General Operation                        |     |

| 9.2.3 | SSC Kernel Registers                     |     |

| 9.2.4 | Interrupts                               |     |

| 9.3   | ASC0                                     |     |

| 9.3.1 | ASC0 Description                         |     |

| 9.3.2 | Features of the ASC0 Controller          |     |

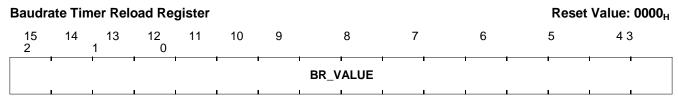

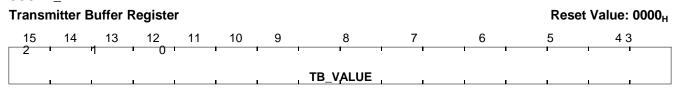

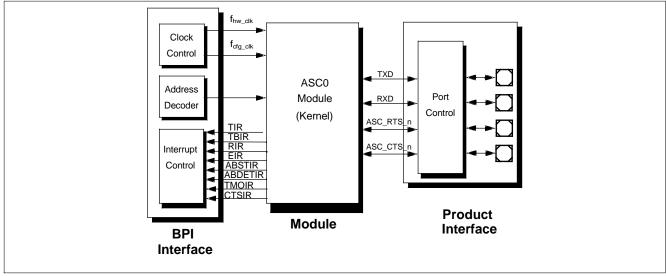

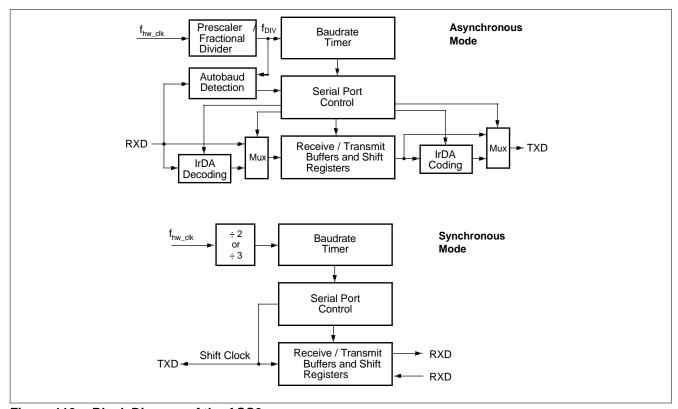

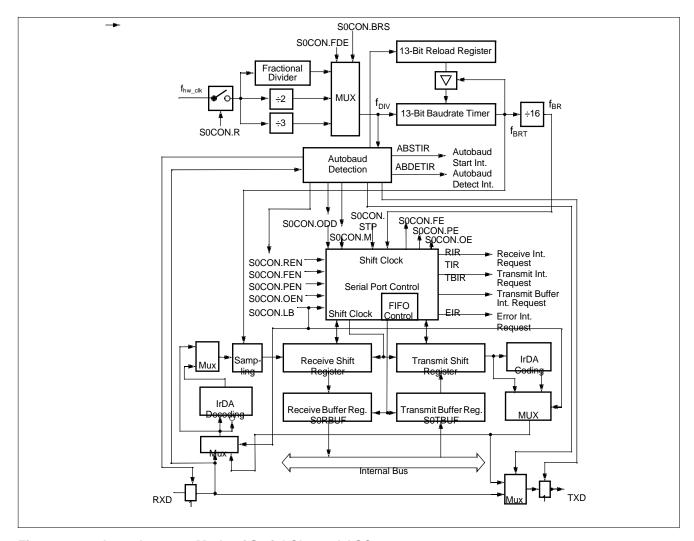

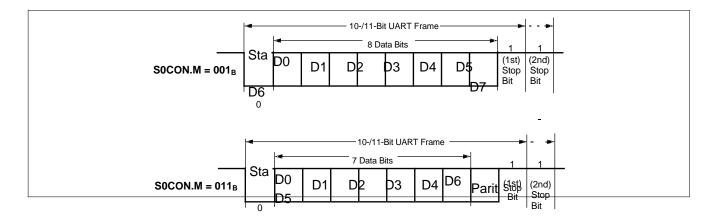

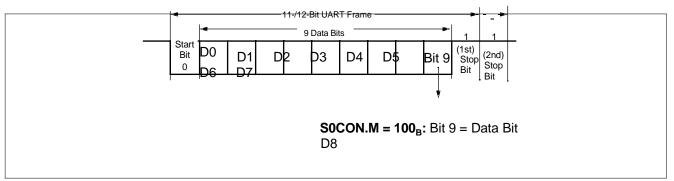

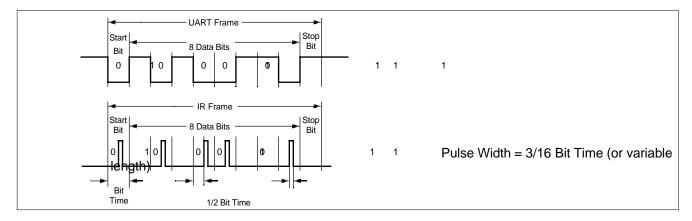

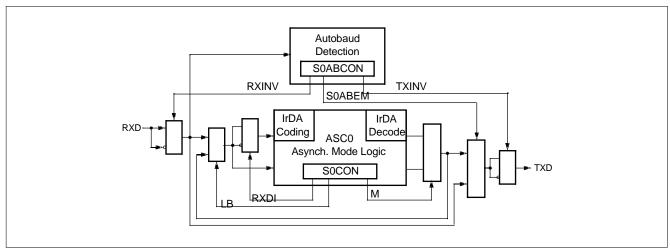

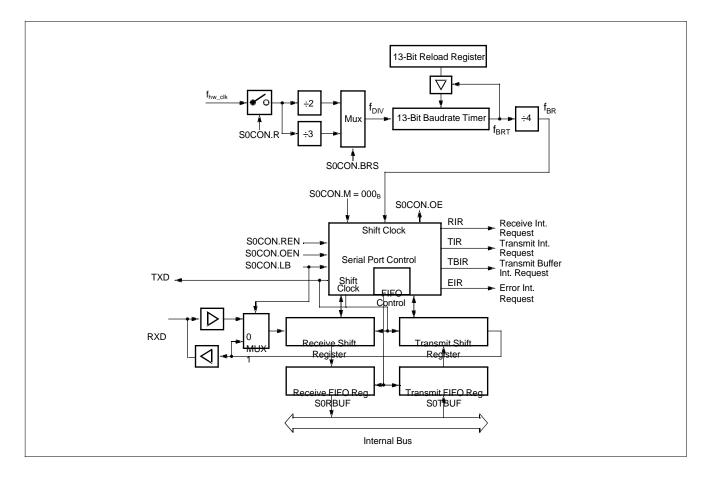

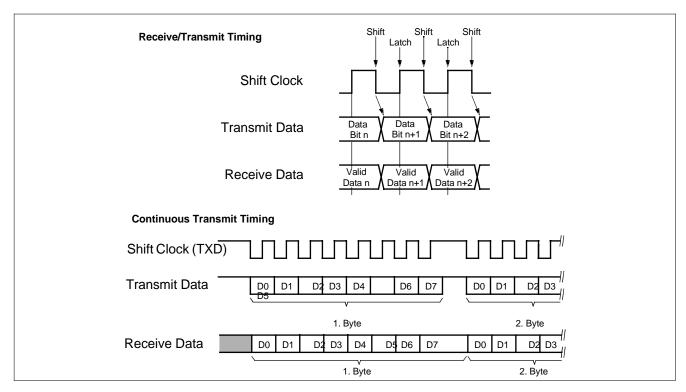

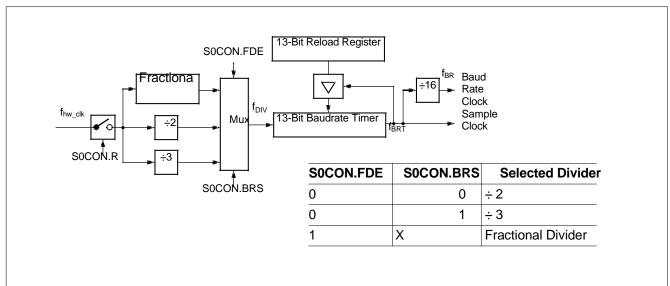

| 9.3.3 | Functional Description of the ASC0       | 307 |

| 9.3.4 | Operational Overview                     | 308 |

| 9.3.5 | General Operation                        | 308 |

| 9.3.6 | Registers                                | 334 |

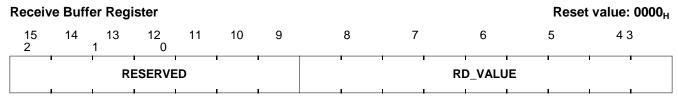

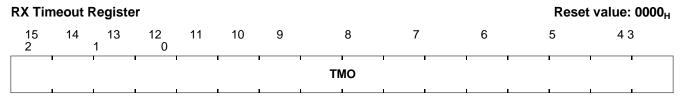

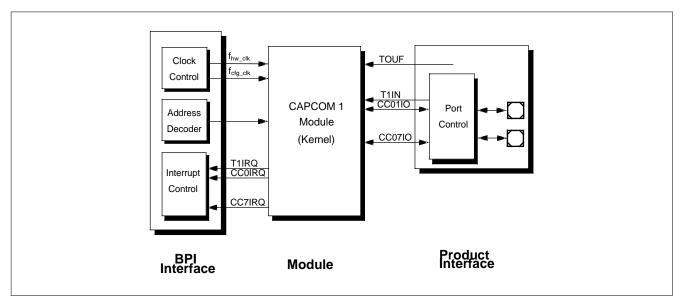

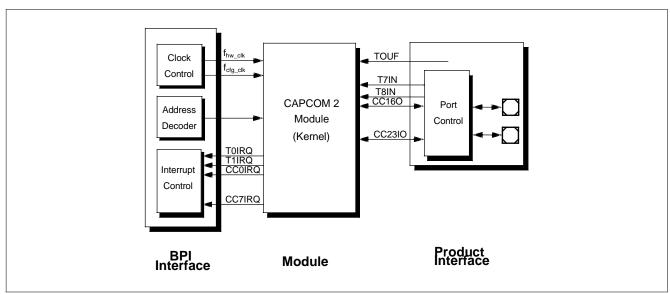

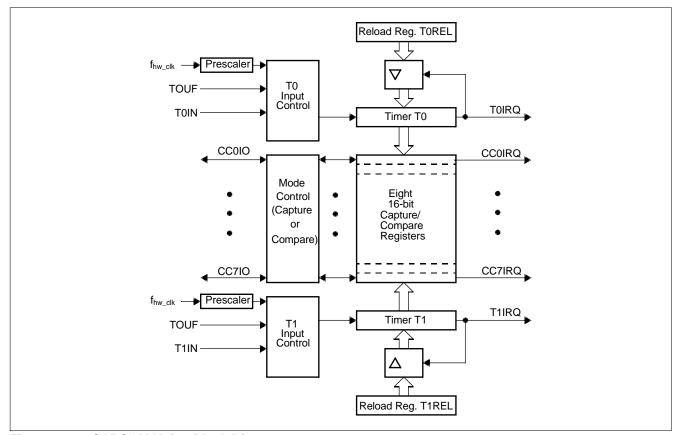

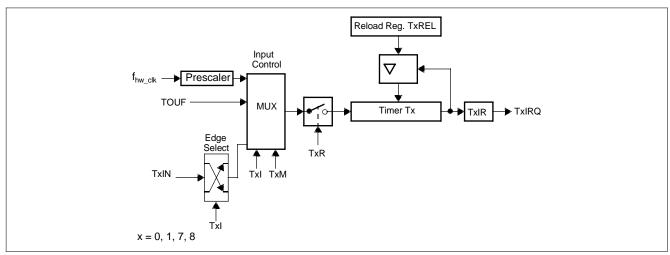

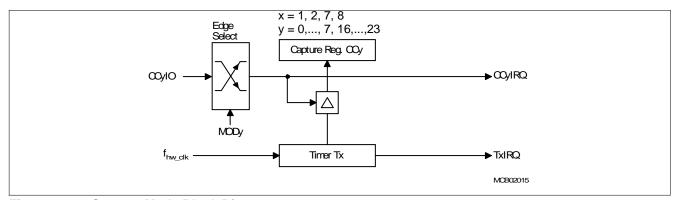

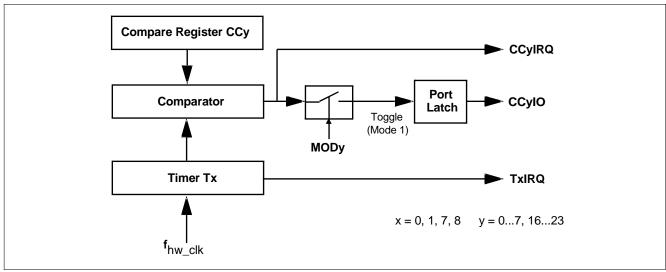

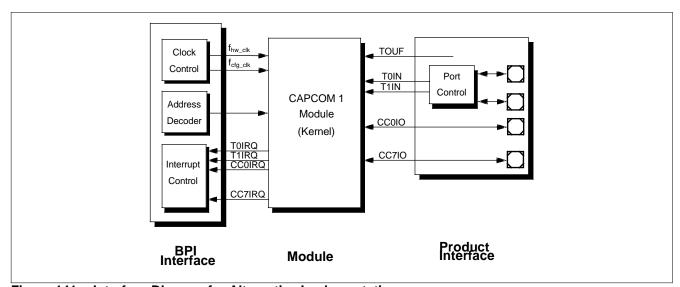

| 9.4   | CAPCOM 1 and 2                           | 347 |

| 9.4.1 | Introduction                             | 347 |

| 9.4.2 | Operational Overview                     | 349 |

| 9.4.3 | Functional Overview                      | 350 |

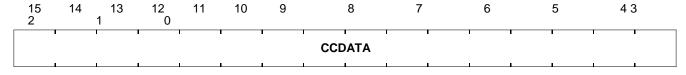

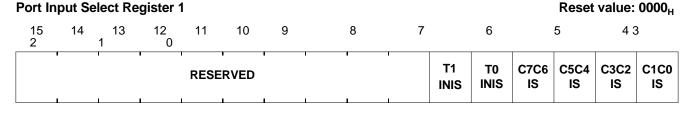

| 9.4.4 | Registers                                | 362 |

| 9.4.5 | Interrupts                               | 375 |

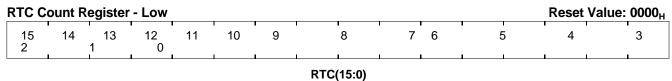

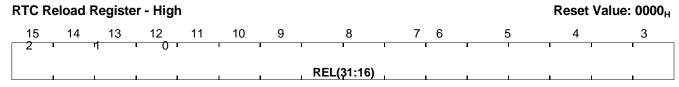

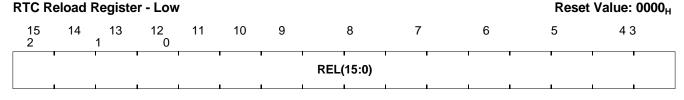

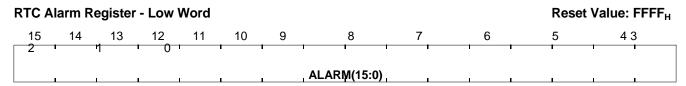

| 9.5   | RTC                                      | 376 |

| 9.5.1 | Introduction                             | 376 |

| 9.5.2 | RTC Register Overview                    | 376 |

| 9.5.3 | RTC Shell                                | 377 |

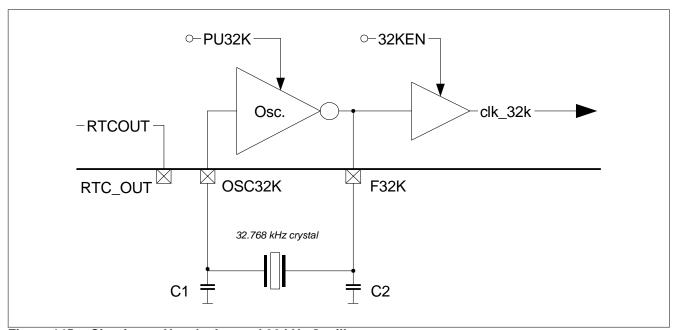

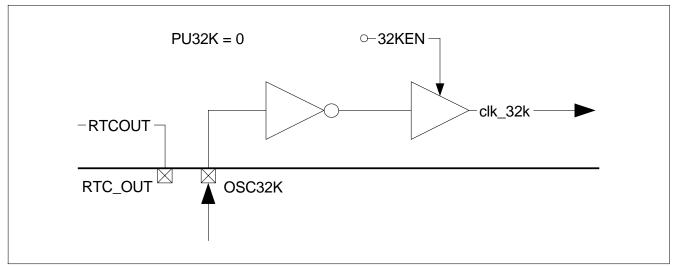

| 9.5.4 | 32k Oscillator                           | 380 |

| 9.5.5 | RTC Macro                                | 382 |

| 9.5.6 | RTC Power Supply Concept                 | 391 |

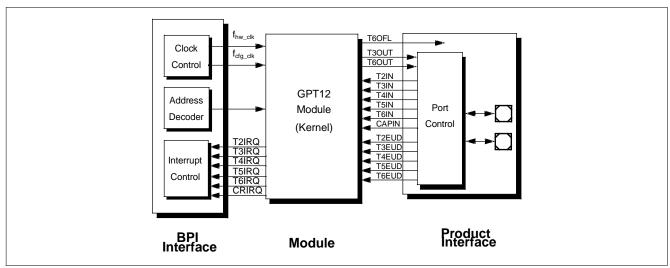

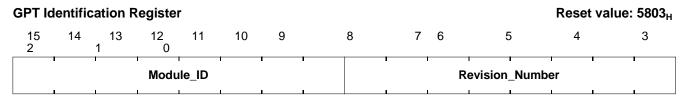

| 9.6   | GPT 1 and 2                              | 392 |

| 9.6.1 | E-GOLDvoice Specific Restrictions        | 392 |

| 9.6.2 | Introduction                             | 392 |

| 9.6.3 | Overview                                 |     |

| 9.6.4 | Kernel Description                       | 393 |

| 9.6.5 | Interrupts                               | 424 |

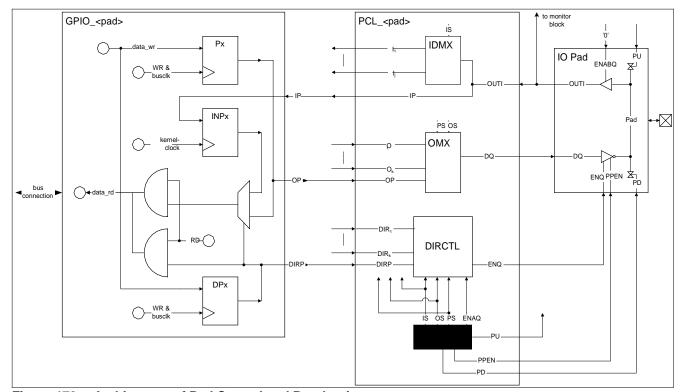

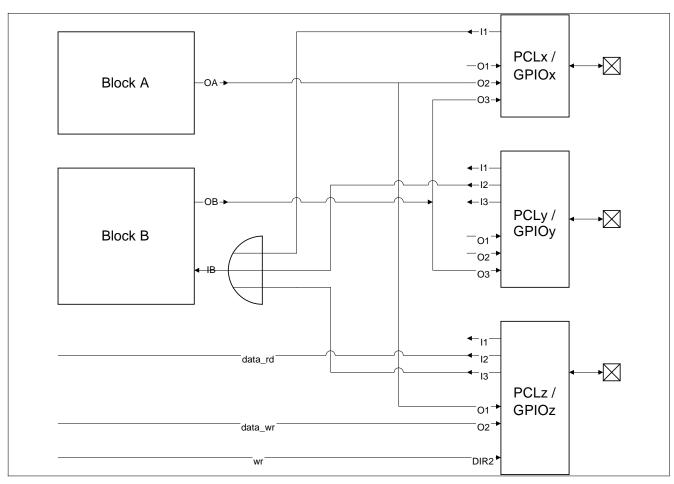

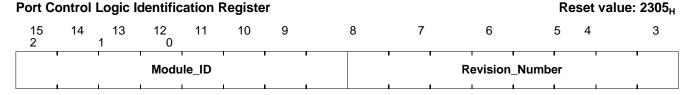

| 9.7   | Port Control Logic                       | 425 |

| 9.7.1                        | Functional Overview                                         | 425   |

|------------------------------|-------------------------------------------------------------|-------|

| 9.7.2                        | Register Description PCL_ <pad></pad>                       | 427   |

| 9.7.3                        | IDMX                                                        | 429   |

| 9.7.4                        | OMX                                                         | 429   |

| 9.7.5                        | DIRCTL                                                      | 429   |

| 9.7.6                        | General Purpose I/O                                         | 430   |

| 9.7.7                        | Control Registers                                           | 431   |

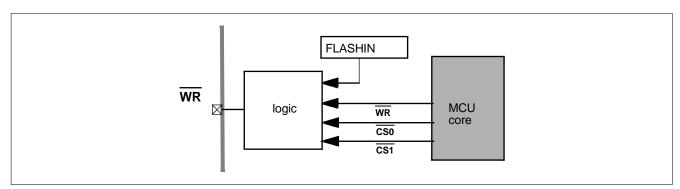

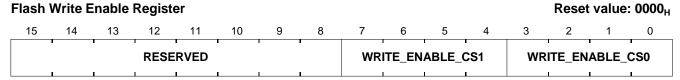

| 9.7.8                        | Flash Overwrite Protection                                  | . 431 |

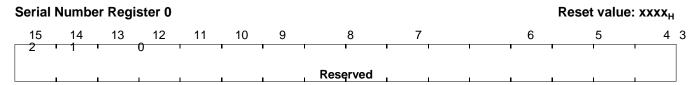

| 9.7.9                        | PCL E-Fuse Boxes and Corresponding Registers                | . 433 |

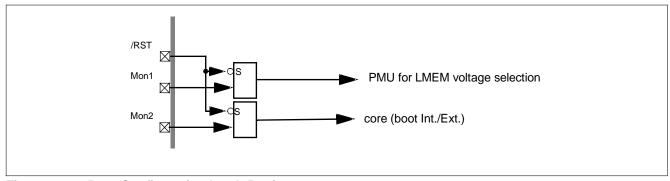

| 9.7.10                       | Internal Signal Monitoring                                  | 435   |

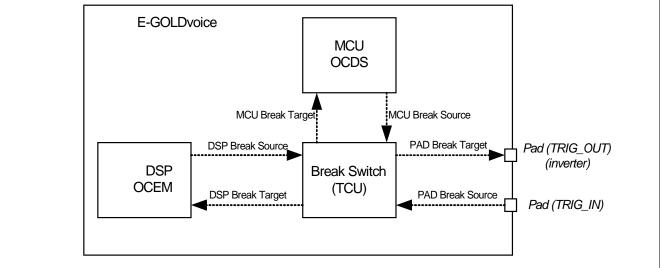

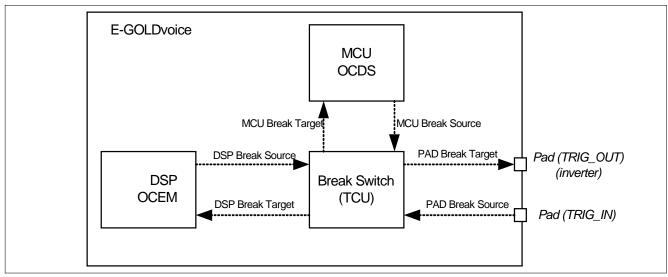

| 9.8                          | TAP Controller and Break Switch                             | 466   |

| 9.8.1                        | Introduction                                                | 466   |

| 9.8.2                        | Break Switch                                                | 466   |

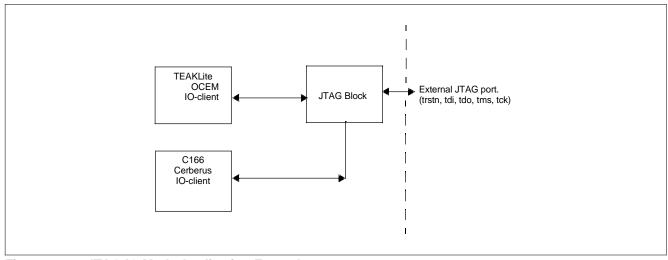

| 9.8.3                        | JTAG                                                        | 469   |

| 10                           | Register Lists and Mapping                                  | 481   |

| 10.1                         | PD-Bus Register Addresses                                   |       |

| 10.1.1                       | Register Addresses                                          |       |

| 10.2                         | X-Bus Register Addresses                                    |       |

| 10.3                         | RF Register Set                                             |       |

|                              | Electrical and Temperature Characteristics                  |       |

| 11                           |                                                             |       |

| 11.1                         | Maximum Values (Destruction limits)                         |       |

| 11.1.1<br>11.1.2             | Maximum ESD                                                 |       |

|                              | Maximum Temperature                                         |       |

| 11.1.3<br>11.1.4             | Maximum Voltages (Digital, Analog and PMU)  Maximum Current |       |

| 11.1. <del>4</del><br>11.1.5 | Absolute Maximum Ratings                                    |       |

| 11.1.5                       | Normal Operation Values                                     |       |

| 11.2.1                       | Static (DC Characteristics)                                 |       |

| 11.2.1                       | Dynamic (AC Characteristics)                                |       |

| 11.3                         | Mixed Signals and Other Values                              |       |

| 11.3.1                       | Audio                                                       |       |

| 11.3.1                       | Measurement Interface                                       |       |

| 11.3.3                       | RF Power Ramping                                            |       |

| 11.3.4                       | AC/DC Characteristics of RF Subsystem                       |       |

| 11.4                         | AC/DC Characteristics of Linear Voltage Regulators          |       |

| 11.4.1                       | LIO Linear Voltage Regulator                                |       |

| 11.4.2                       | LANA Linear Voltage Regulator                               |       |

| 11.4.3                       | LRFRX Linear Voltage Regulator                              |       |

| 11.4.4                       | LRFTRX Linear Voltage Regulator                             |       |

| 11.4.5                       | LRFXO Linear Voltage Regulator                              |       |

| 11.4.6                       | LRTC Linear Voltage Regulator                               |       |

| 11.4.7                       | LD1 Linear Voltage Regulator                                |       |

| 11.4.8                       | LSIM Linear Voltage Regulator                               |       |

| 11.4.9                       | LMEM Linear Voltage Regulator                               |       |

| 11.4.10                      | LBUF Linear Voltage Regulator                               |       |

| 11.5                         | Regulator Parameter Definition                              |       |

| 11.5.1                       | Line Regulation and Transient Line Regulation               |       |

| 11.5.2                       | Load Regulation and Transient Load Regulation               |       |

| 11.5.3                       | Dropout Definition                                          |       |

| 11.5.4                       | PSRR Definition                                             | 577   |

| 11.6   | AC/DC Characteristics of Charger Components |

|--------|---------------------------------------------|

| 11.6.1 | Shunt Regulator                             |

| 11.6.2 | Over-Voltage Detection 578                  |

| 11.6.3 | VBAT Power On 578                           |

| 11.6.4 | Battery Voltage Supervision Unit 579        |

| 11.6.5 | Backlight Comparator                        |

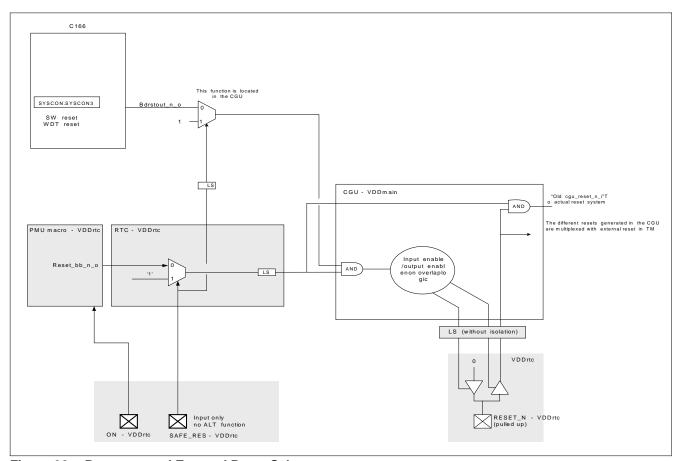

| 12     | <b>System Reset</b>                         |

| 12.1   | Introduction                                |

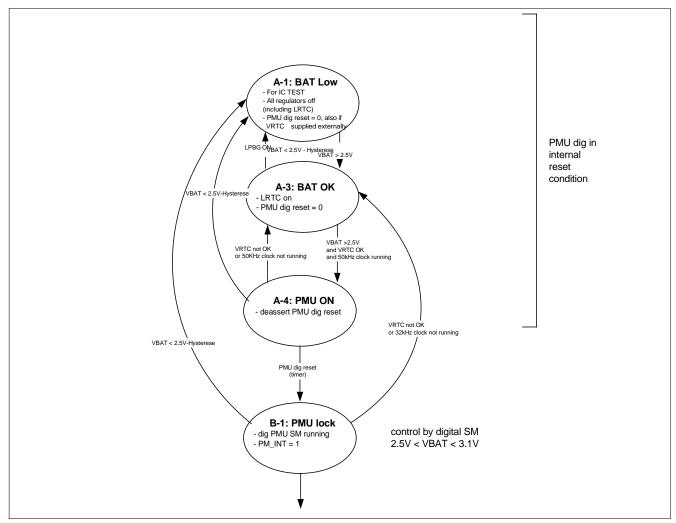

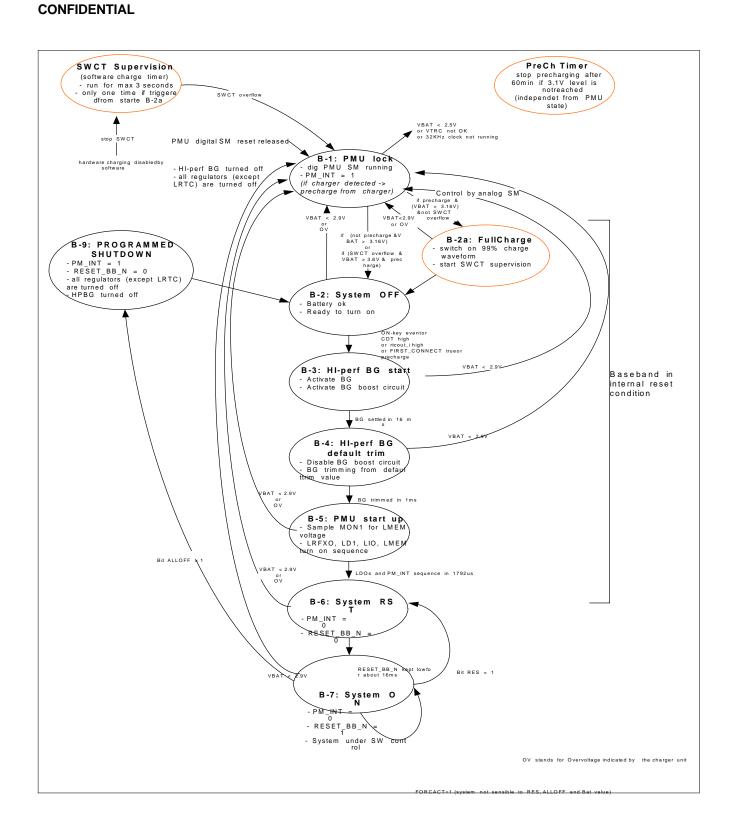

| 12.1.1 | PMU Reset 581                               |

| 12.1.2 | Software Reset 581                          |

| 12.1.3 | Watchdog Timer Reset                        |

| 12.1.4 | Reset of RTC, SIM Cards, DSP, and Analog    |

| 12.1.5 | CGU Reset Block                             |

| 12.2   | Reset                                       |

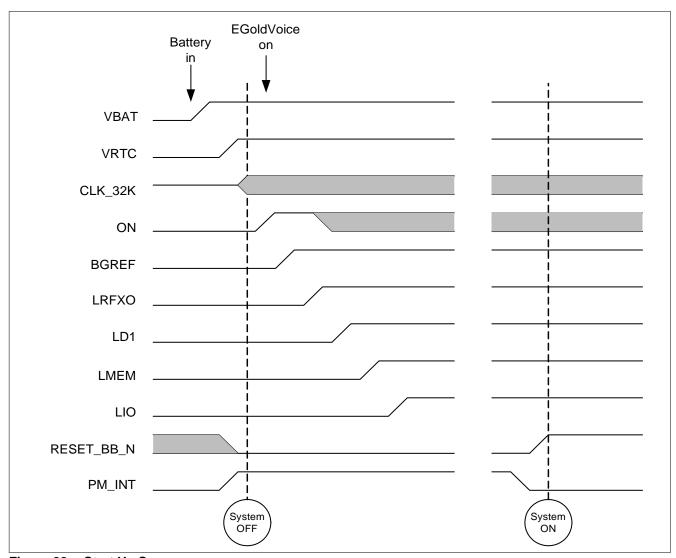

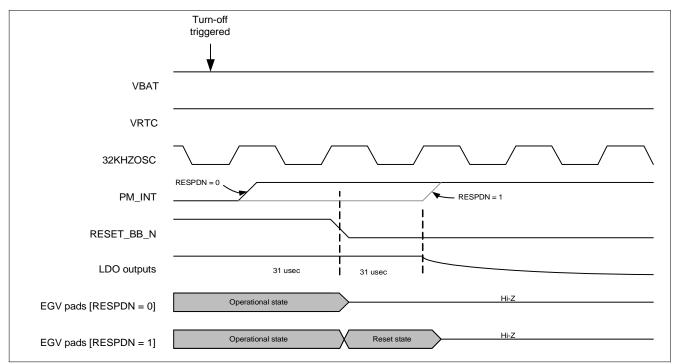

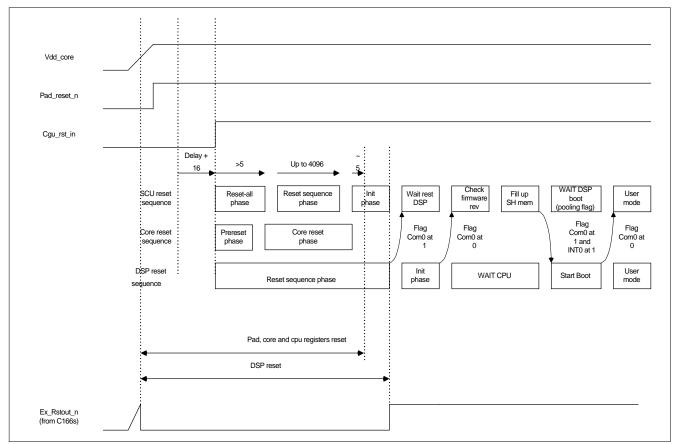

| 12.2.1 | Reset Timing Diagrams                       |

| 12.2.2 | Power On/Off Sequences                      |

| 12.2.3 | CPU Boot Configuration                      |

| 13     | <b>Debug</b>                                |

## **List of Figures**

# **List of Figures**

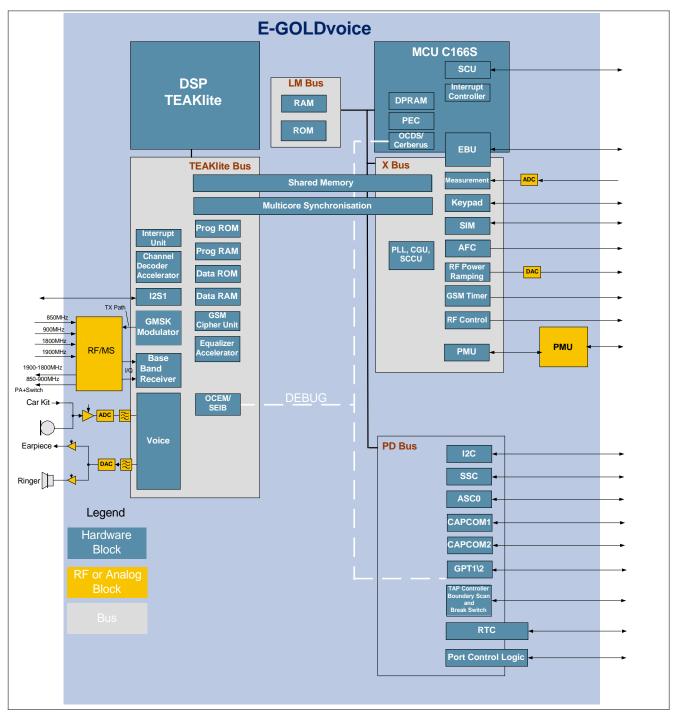

| Figure 1  | E-GOLDvoice Block Diagram                                                 | . 21  |

|-----------|---------------------------------------------------------------------------|-------|

| Figure 2  | Typical E-GOLDvoice Application Circuit                                   | 23    |

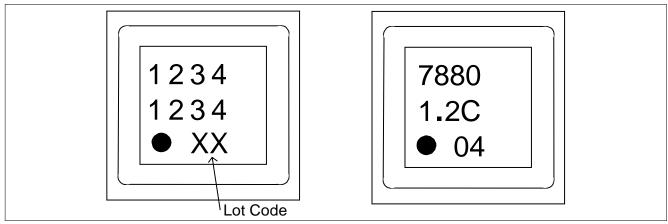

| Figure 3  | Package Label                                                             | . 27  |

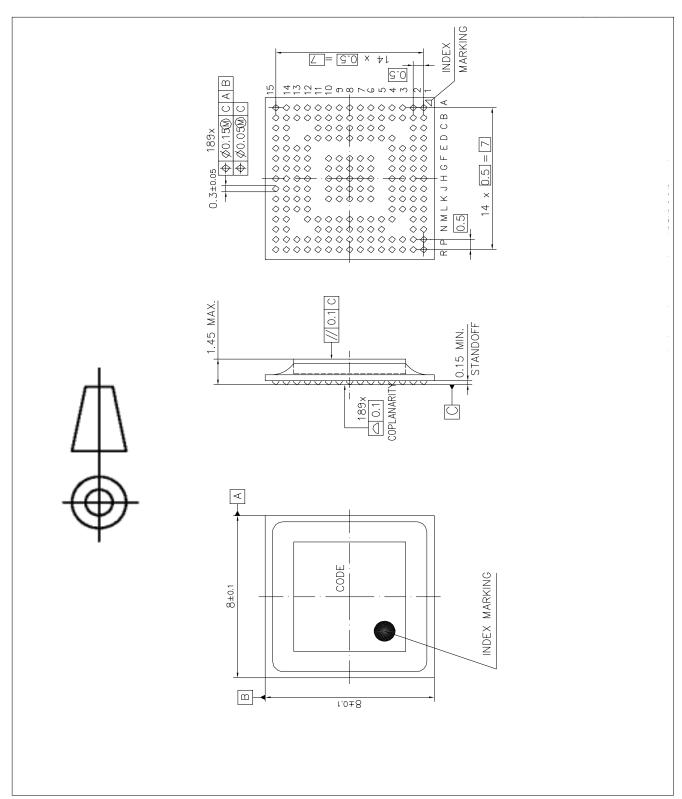

| Figure 4  | E-GOLDvoice: SG-LF2BGA-189-1 Package Details and Ball Labelling           | 28    |

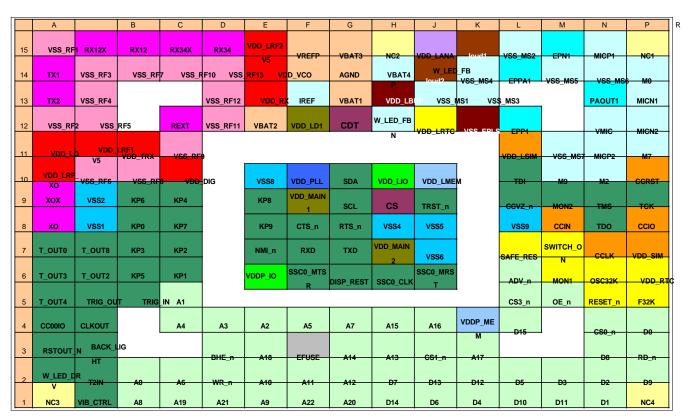

| Figure 5  | Legend for E-GOLDvoice Ballout                                            | 29    |

| Figure 6  | E-GOLDvoice Ballout Viewed from Above the Chip                            | 30    |

| Figure 7  | Diagram of E-GOLDvoice Buses                                              | 38    |

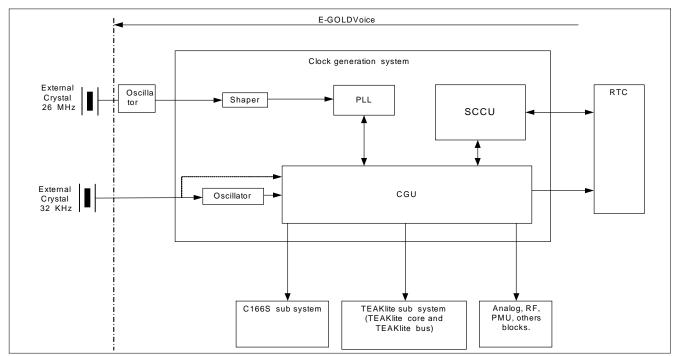

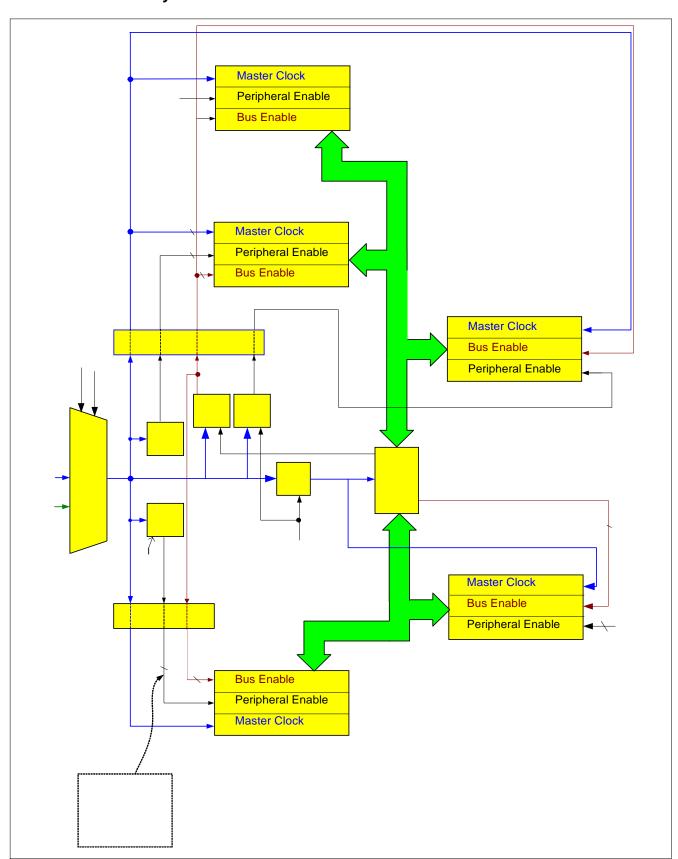

| Figure 8  | Clock Distribution                                                        | . 46  |

| Figure 9  | E-GOLDvoice Transceiver State Machine Modes                               | 55    |

| Figure 10 | RX Sequencer Timing                                                       | . 56  |

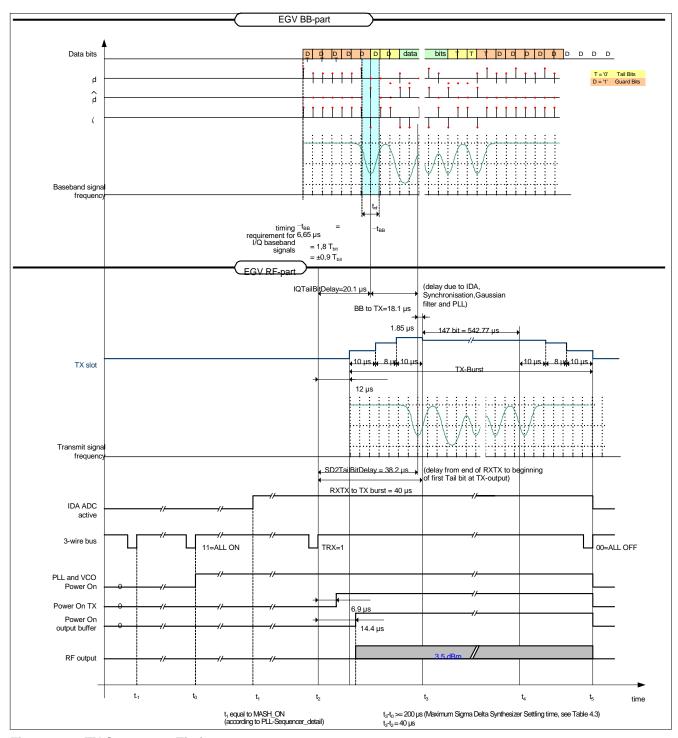

| Figure 11 | TX Sequencer Timing                                                       | . 57  |

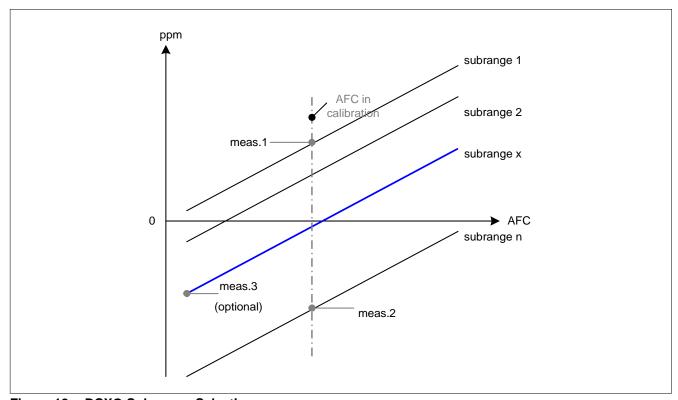

| Figure 12 | DCXO Sub-range Selection                                                  | . 58  |

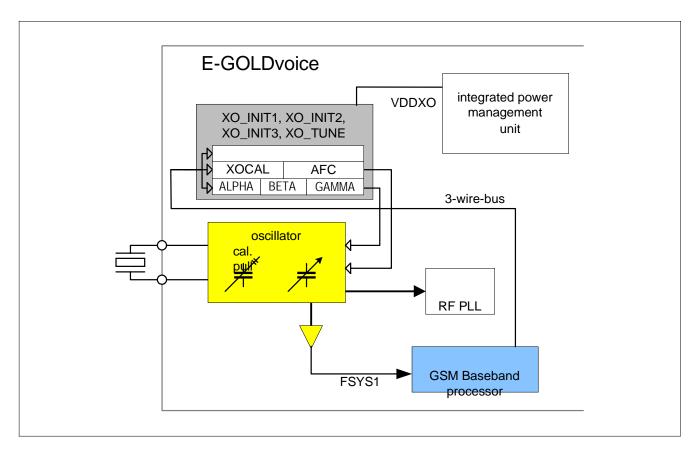

| Figure 13 | Crystal Oscillator Functional Overview                                    | 59    |

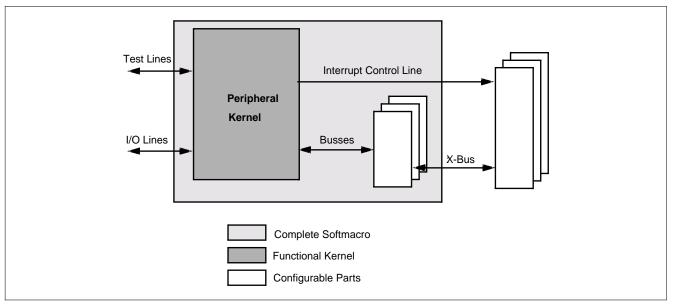

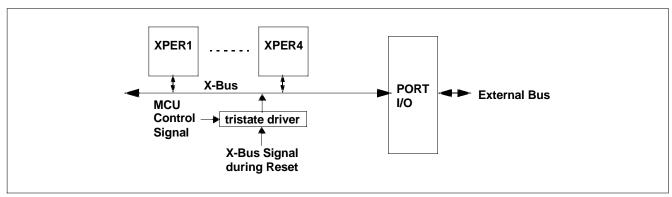

| Figure 14 | General Block Diagram of X-Bus Peripheral                                 | 60    |

| Figure 15 | MCU Configuration during Reset via X-Bus                                  | . 61  |

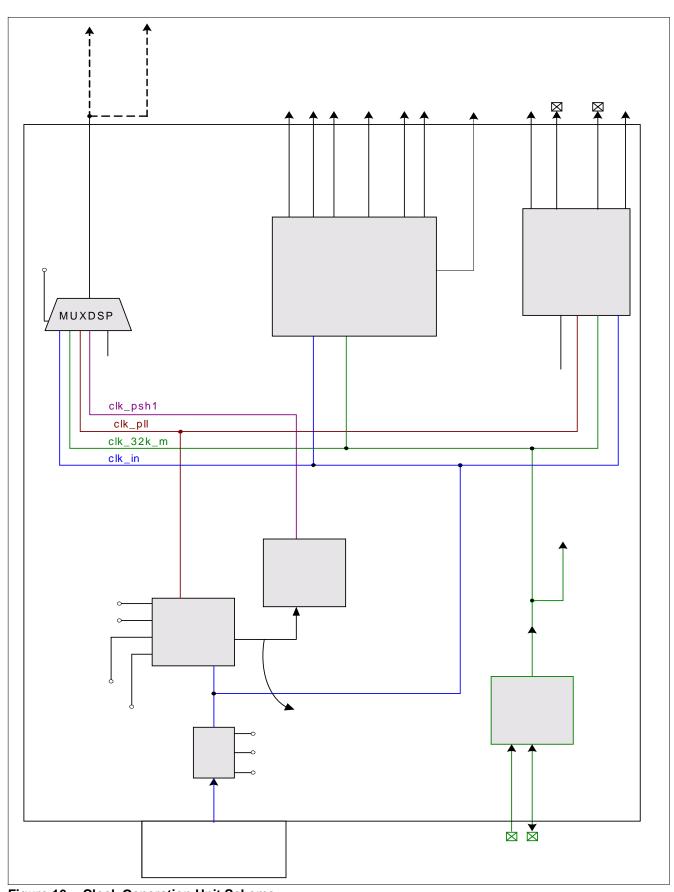

| Figure 16 | Clock Generation Unit Scheme                                              |       |

| Figure 17 | Overview of E-GOLDvoice CPU Clock Generation System                       | 64    |

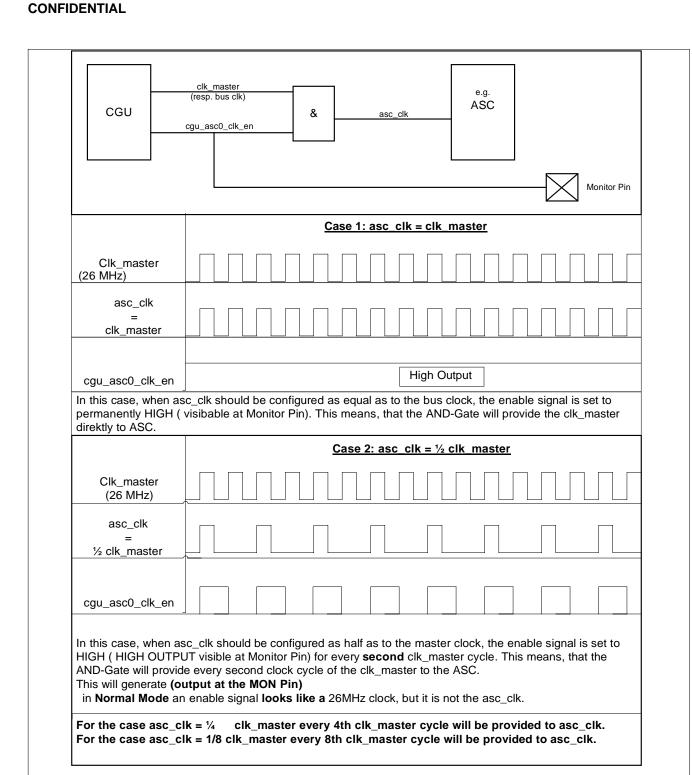

| Figure 18 | Clock Enable                                                              |       |

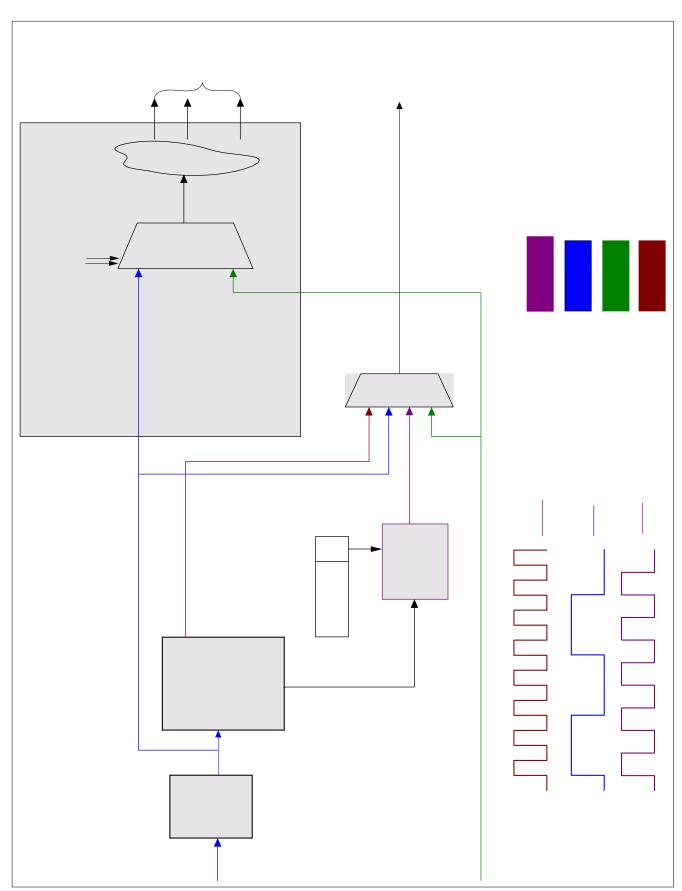

| Figure 19 | Clock and Enable Generation for MCU Sub-System                            | 71    |

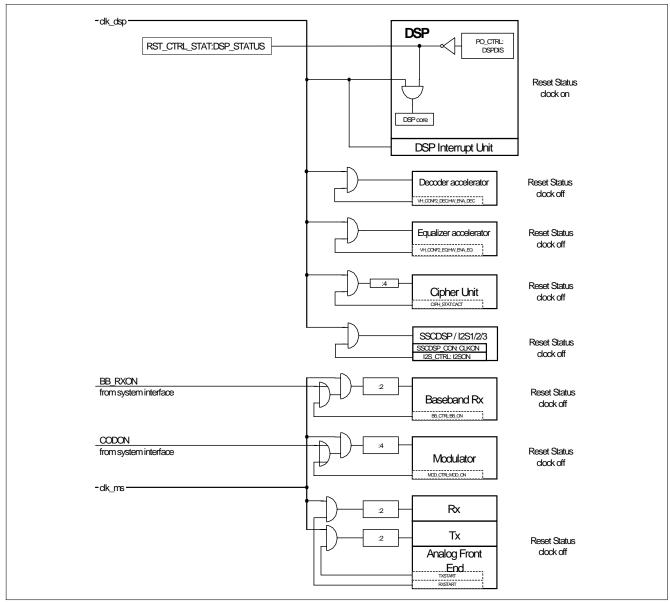

| Figure 20 | Generation of Clocks for the DSP Section                                  |       |

| Figure 21 | Overview of Interface Control Functions                                   | 85    |

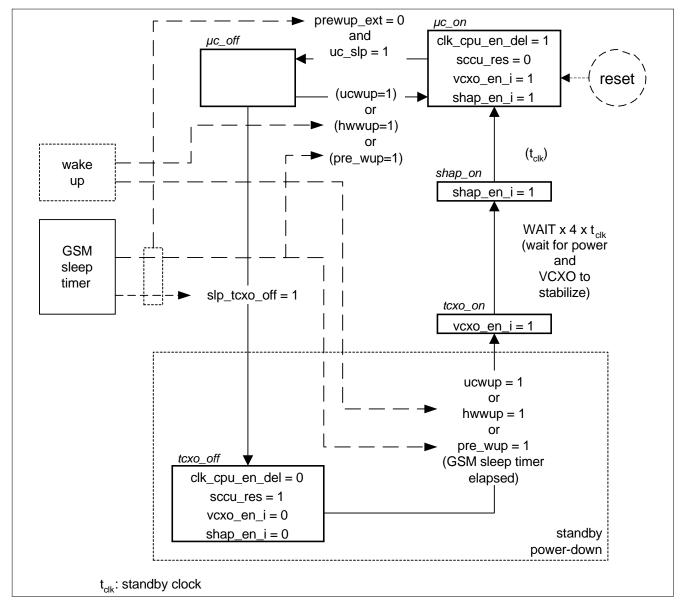

| Figure 22 | SCCU Main State Machine                                                   | 86    |

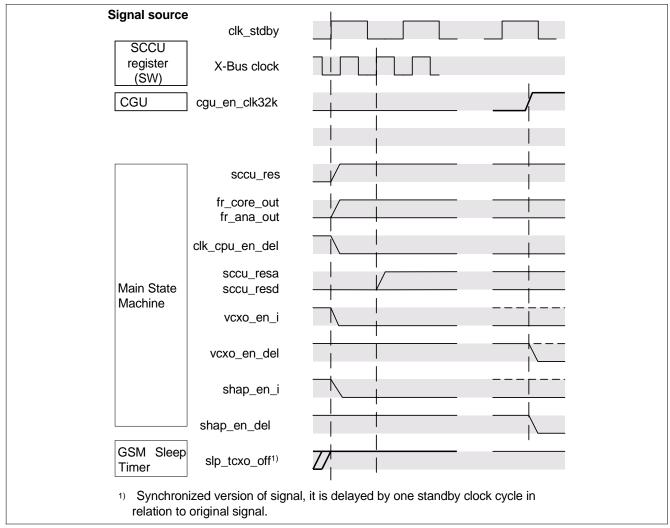

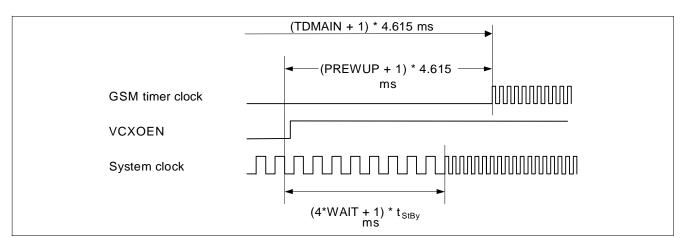

| Figure 23 | Function of Signals from GSM Sleep Timer                                  | 87    |

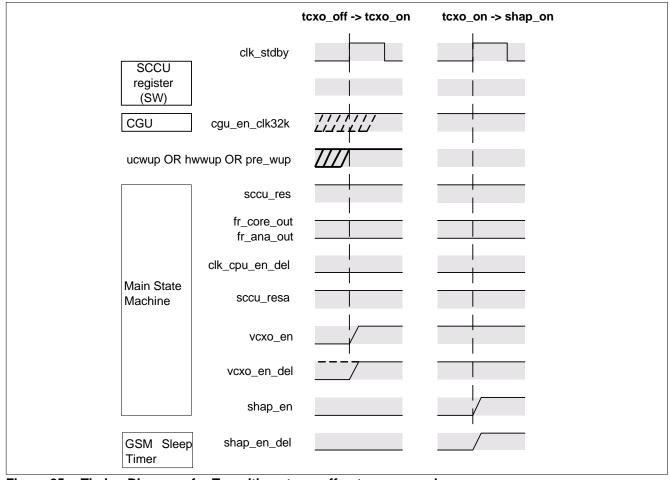

| Figure 24 | Timing Diagram for Transition µc_off -> tcxo_off                          | . 88  |

| Figure 25 | Timing Diagrams for Transitions tcxo_off -> tcxo_on -> shap_on            | 89    |

| Figure 26 | Timing of Wake-Up Phase                                                   | 90    |

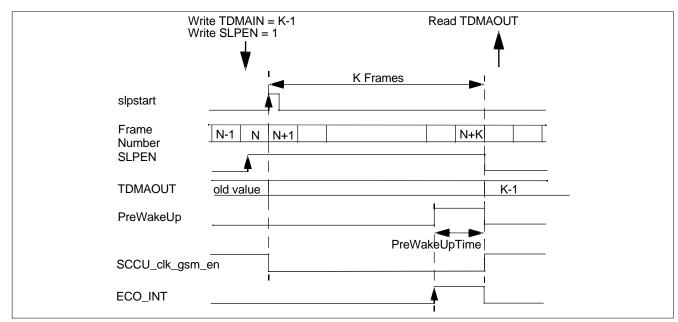

| Figure 27 | Sleep Function Timing Diagram                                             | 92    |

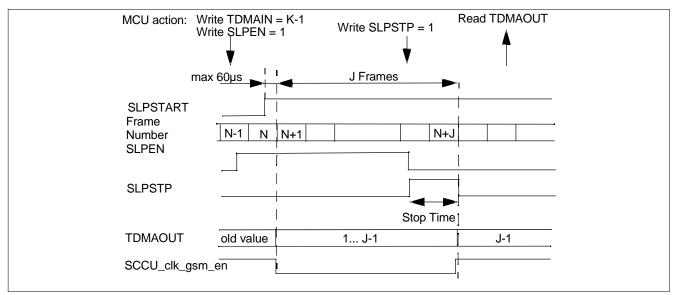

| Figure 28 | Early Termination of GSM Timer Sleep Phase                                | 93    |

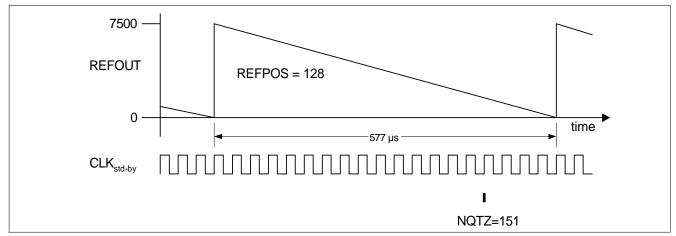

| Figure 29 | Stand-By Clock Calibration                                                | . 94  |

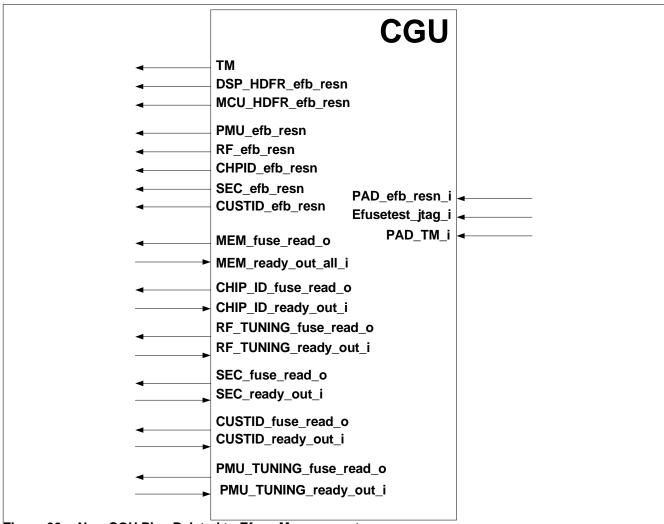

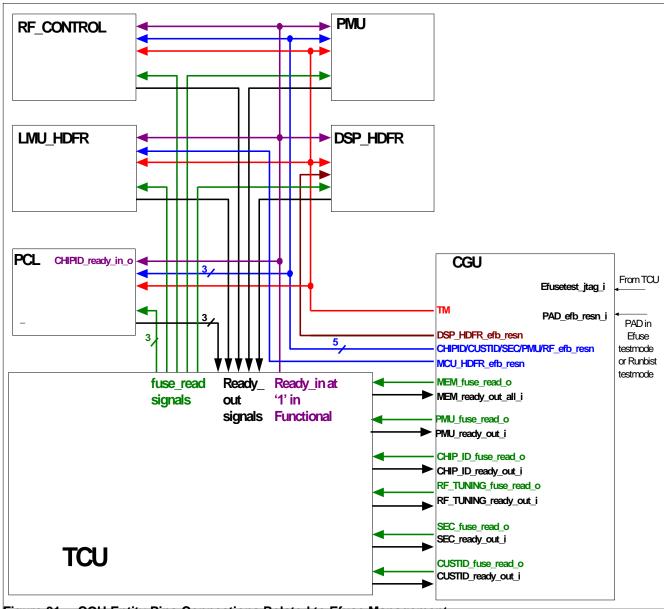

| Figure 30 | New CGU Pins Related to Efuse Management                                  | . 104 |

| Figure 31 | CGU Entity Pins Connections Related to Efuse Management                   | . 105 |

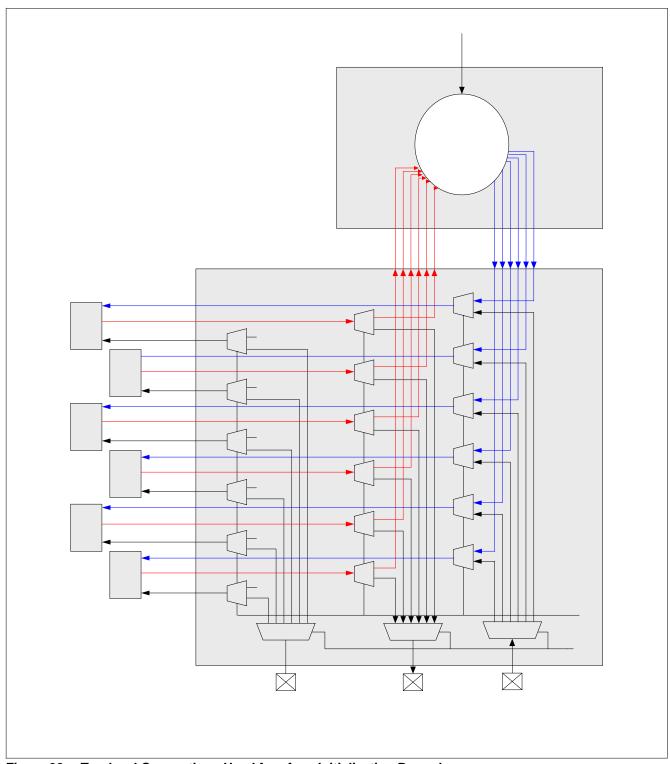

| Figure 32 | Top-level Connections Used for efuse Initialization Procedure             | 107   |

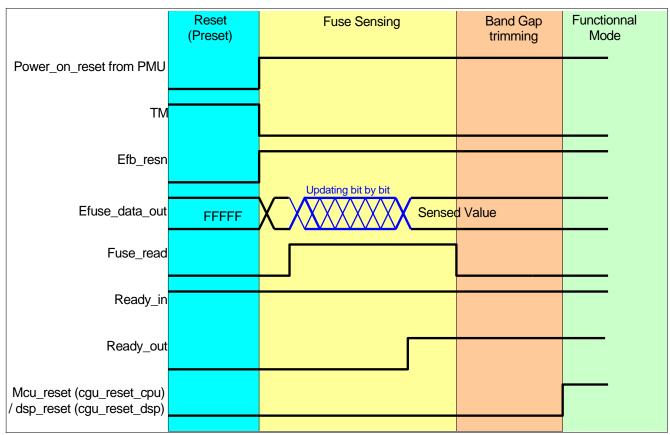

| Figure 33 | Functional Timing Diagram for Initialization Procedure at efuse Box Level | . 108 |

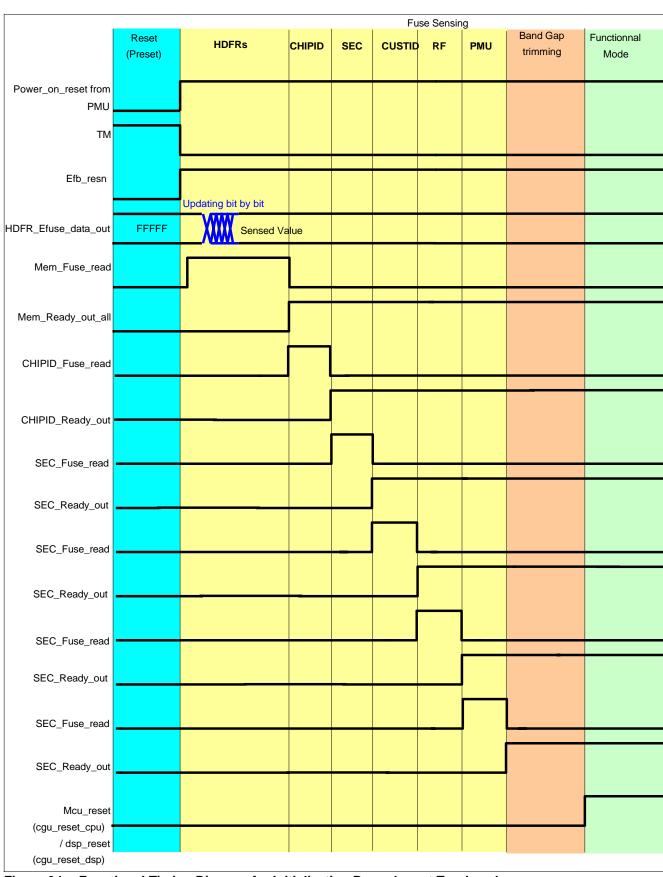

| Figure 34 | Functional Timing Diagram for Initialization Procedure at Top-Level       | . 109 |

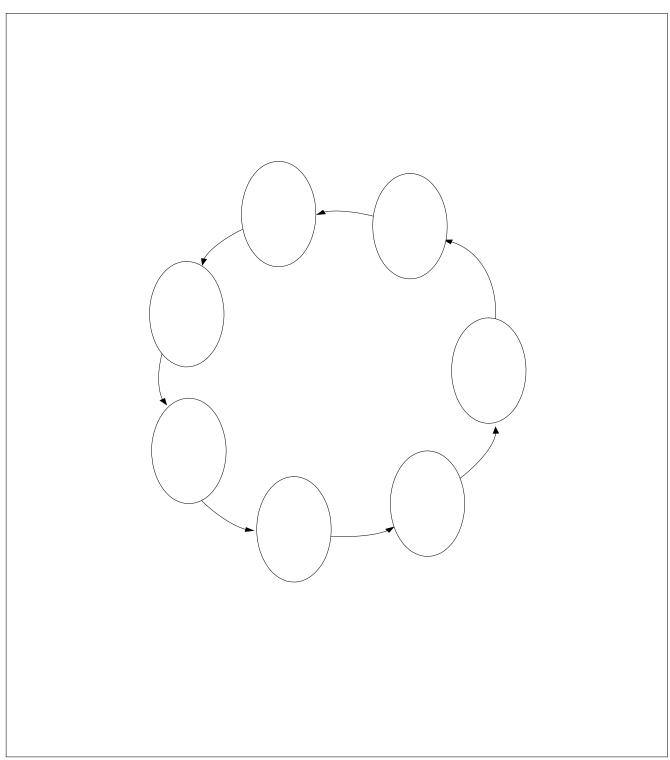

| Figure 35 | Initialization Efuse Sensing State Machine                                | 110   |

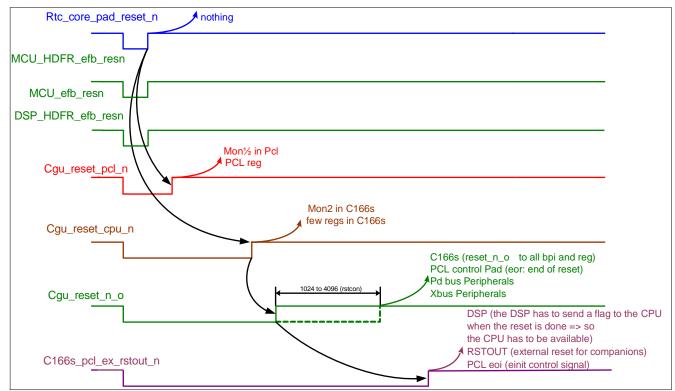

| Figure 36 | Global Hardware Reset Sequence                                            | . 111 |

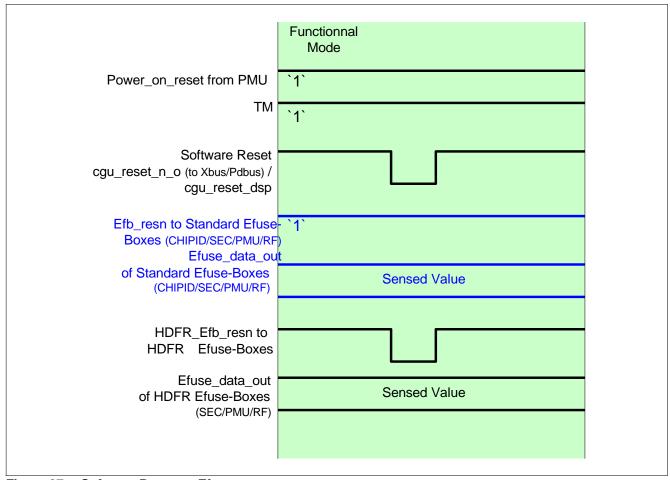

| Figure 37 | Software Reset on Efuses                                                  |       |

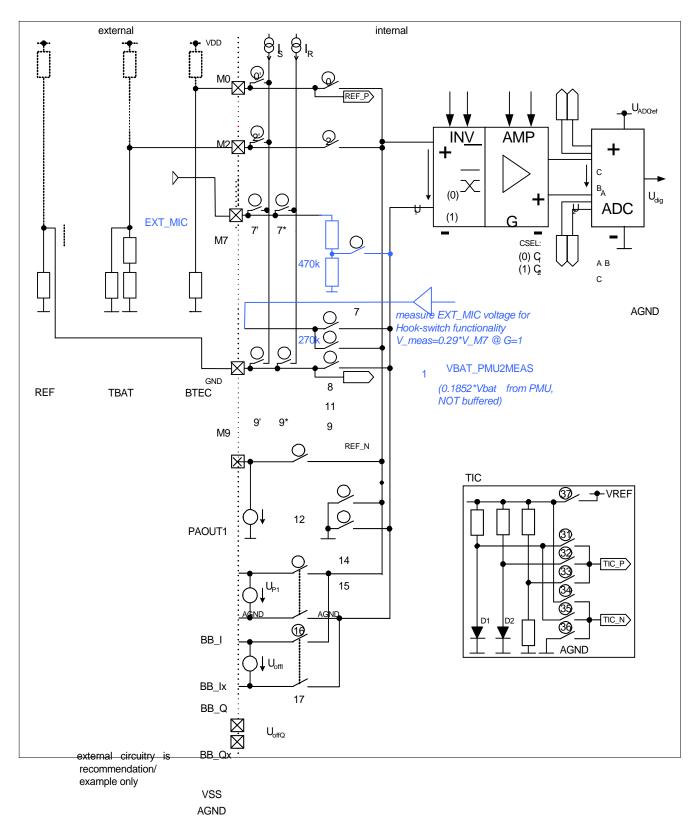

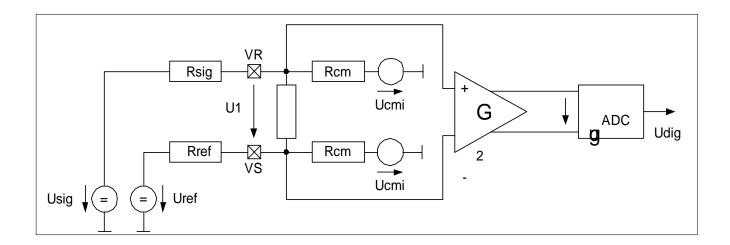

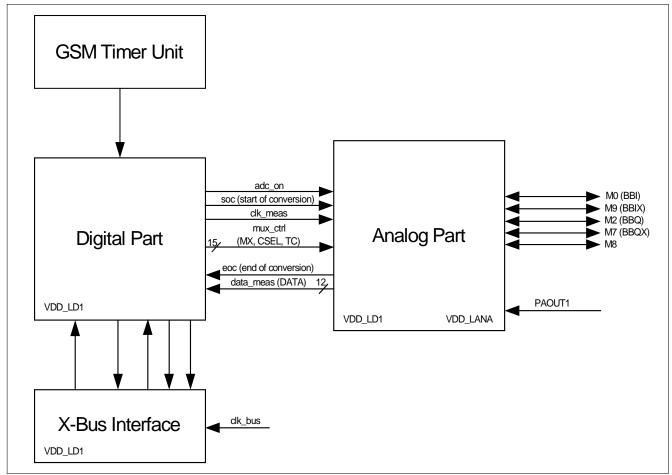

| Figure 38 | Measurement Circuit and Mode Setting                                      | . 115 |

| Figure 39 | Equivalent Network for Differential Measurement Circuit                   | . 118 |

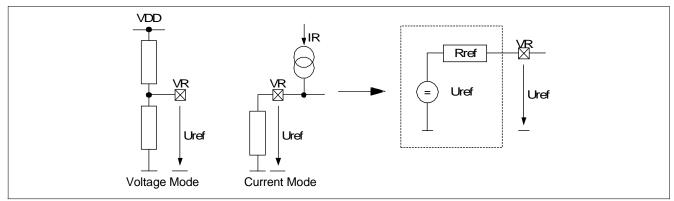

| Figure 40 | Equivalent Network for Reference Voltage Generation                       | . 119 |

| Figure 41 | Equivalent Network for Measurement Signal Input                           | 119   |

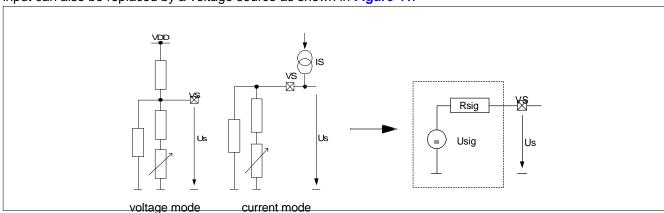

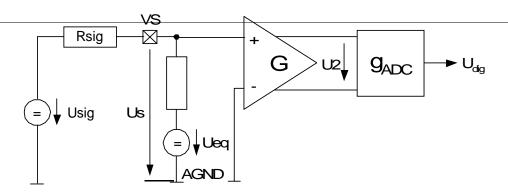

| Figure 42 | Equivalent Network for Single-Ended Measurement Mx                        | . 120 |

| Figure 43 | Equivalent Network for Measurement Signal Input                           | 121   |

| Figure 44 | PAOUT Offset Measurement                                                  | . 123 |

| Figure 45 | Equivalent Network for Offset Calculation                                 | . 124 |

| Figure 46 | Logic Block Diagram of Measurement Interface                              |       |

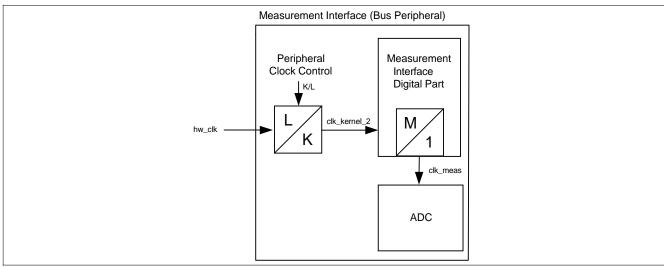

| Figure 47 | Clock Control for Measurement Interface                                   |       |

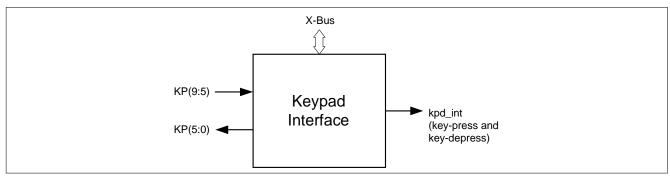

| Figure 48 | Block Symbol of the Keypad Interface                                      |       |

| Figure 49 | Block Diagram of the Internal Keypad Port Circuitry                       | . 142 |

| CONFIDENTIAL | List of Figures |

|--------------|-----------------|

|              |                 |

| Figure 5 | ·                                                         |       |

|----------|-----------------------------------------------------------|-------|

| Figure 5 | SIM Card Interface Block Diagram                          | 146   |

| Figure 5 | 2 Timing of Automatic Power Down Sequence                 | 157   |

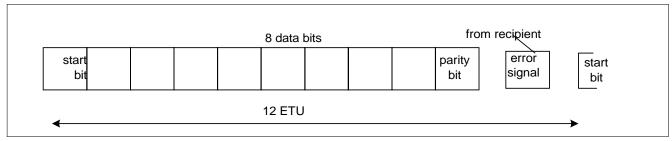

| Figure 5 | SIM Character Data Structure                              | . 158 |

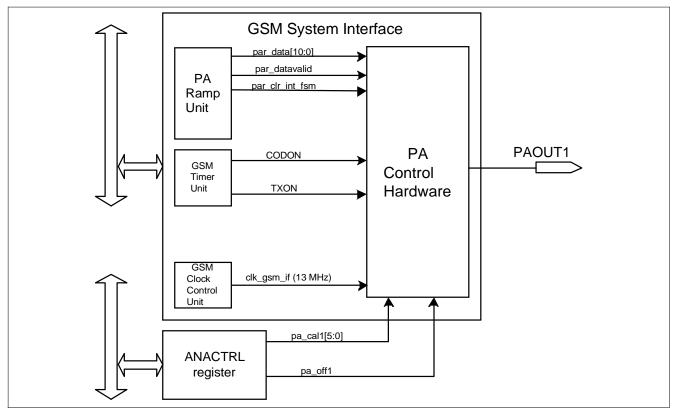

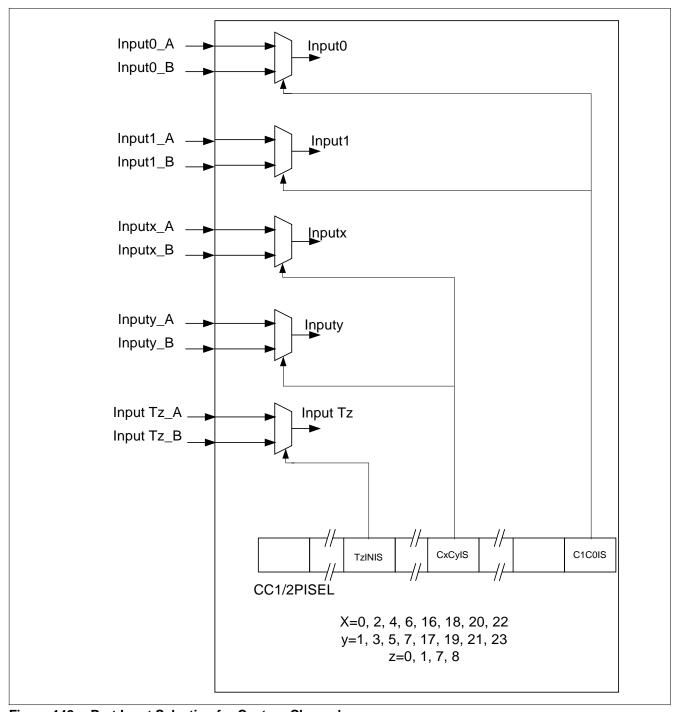

| Figure 5 | Power Amplifier Control Hardware System Overview          | . 162 |

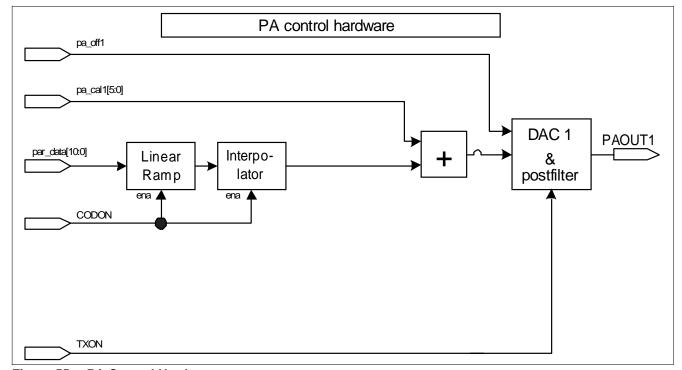

| Figure 5 | 5 PA Control Hardware                                     | 163   |

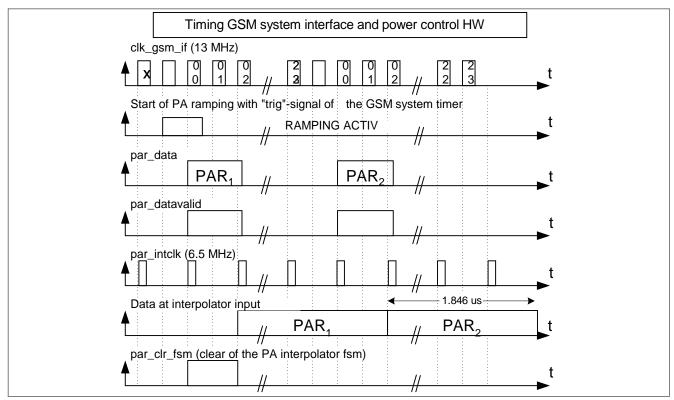

| Figure 5 | S Power Ramping Shapes                                    | 164   |

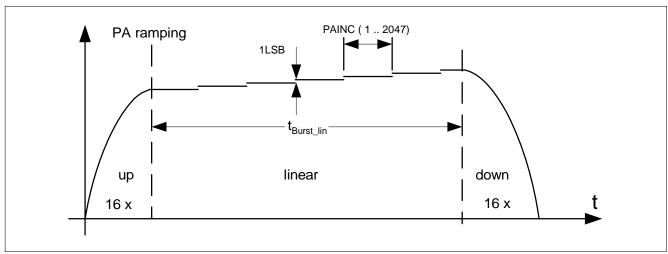

| Figure 5 | 7 Linear Power Ramping during Active Part of the Burst    | 165   |

| Figure 5 | Programming Sequence for Power Ramping                    | 166   |

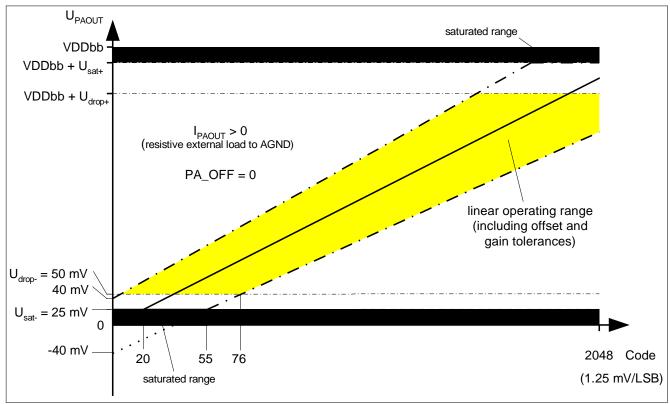

| Figure 5 | Operating Range of PAOUT1 Output after Offset Calibration | . 167 |

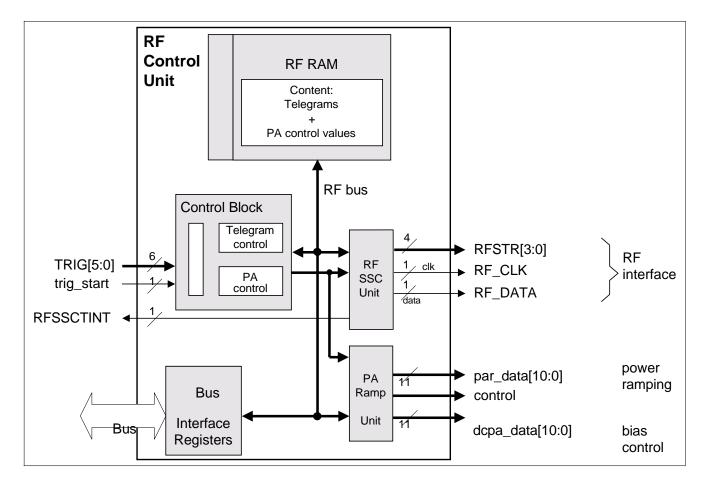

| Figure 6 | RF Control Unit                                           | 170   |

| Figure 6 | Principle Timings of 8 Bit Telegrams                      | . 179 |

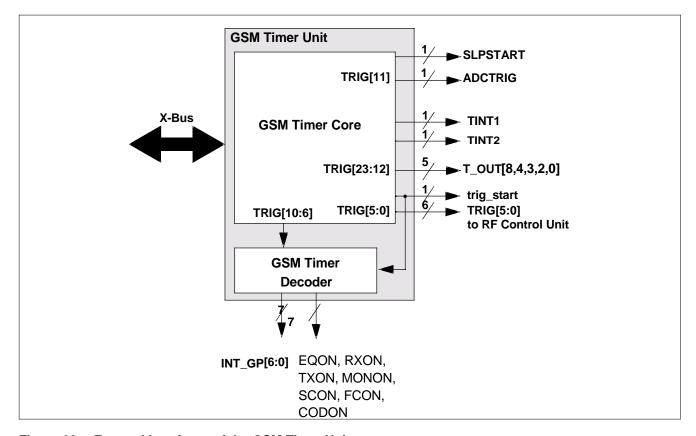

| Figure 6 | 2 External Interfaces of the GSM Timer Unit               | 181   |

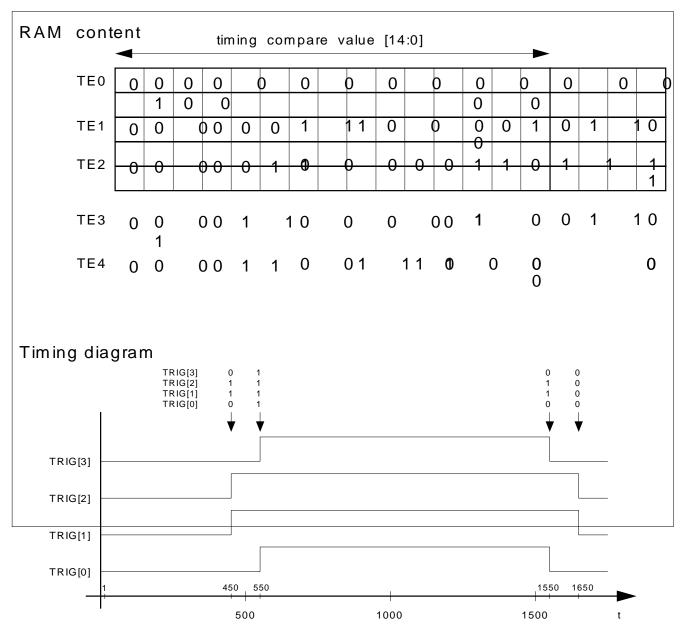

| Figure 6 | Basic Operation of the GSM Timer Unit                     | 183   |

| Figure 6 | •                                                         |       |

| Figure 6 |                                                           |       |

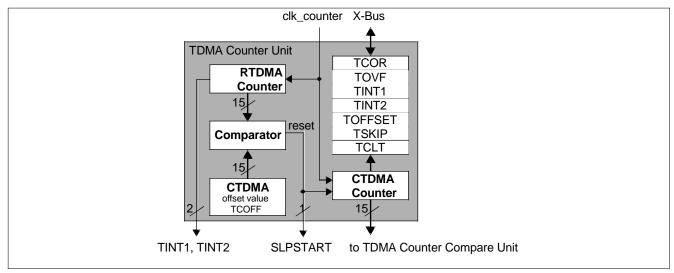

| Figure 6 |                                                           | 196   |

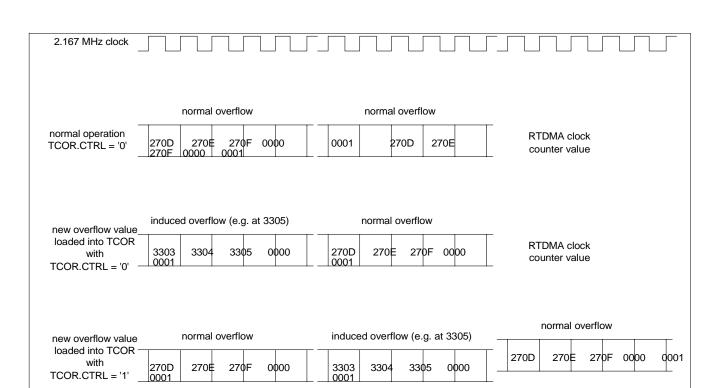

| Figure 6 |                                                           |       |

| Figure 6 |                                                           |       |

| Figure 6 | ·                                                         |       |

| Figure 7 | ·                                                         |       |

| Figure 7 | ·                                                         |       |

| Figure 7 | , .                                                       |       |

| Figure 7 | ,                                                         |       |

| Figure 7 | • •                                                       |       |

| Figure 7 | • ,                                                       |       |

| Figure 7 | ·                                                         |       |

| Figure 7 | · · · · · · · · · · · · · · · · · · ·                     |       |

| Figure 7 |                                                           |       |

| Figure 7 |                                                           |       |

| Figure 8 |                                                           |       |

| Figure 8 | •                                                         |       |

| Figure 8 |                                                           |       |

| Figure 8 |                                                           |       |

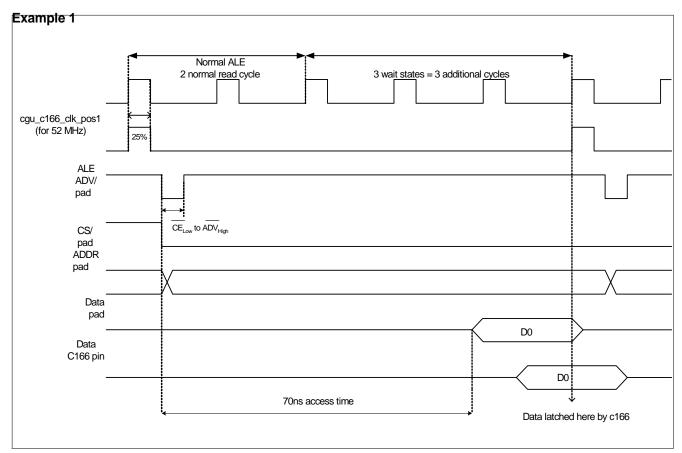

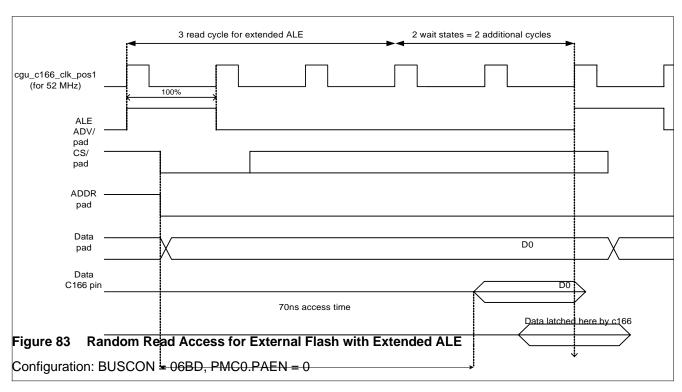

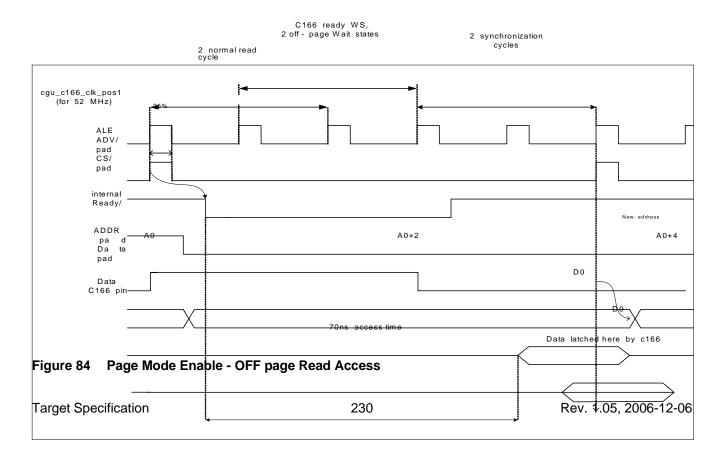

| Figure 8 |                                                           | 230   |

| Figure 8 |                                                           |       |

| Figure 8 | ·                                                         |       |

| Figure 8 | · · ·                                                     |       |

| Figure 8 | · ·                                                       |       |

| Figure 8 | ·                                                         | 249   |

| Figure 9 |                                                           |       |

| Figure 9 |                                                           | 266   |

| Figure 1 |                                                           | 267   |

| CONFIDENTIAL | List of Figure 2 |

|--------------|------------------|

| CONFIDENTIAL | List of Figures  |

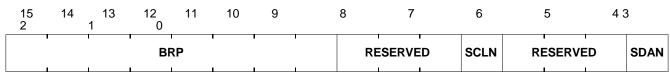

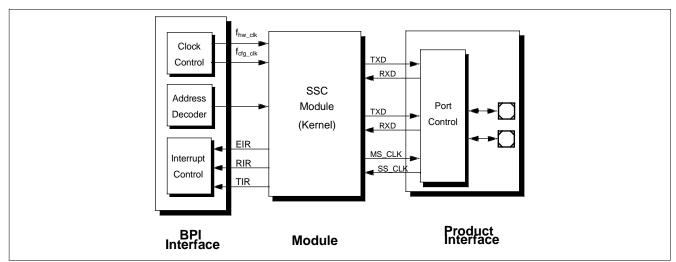

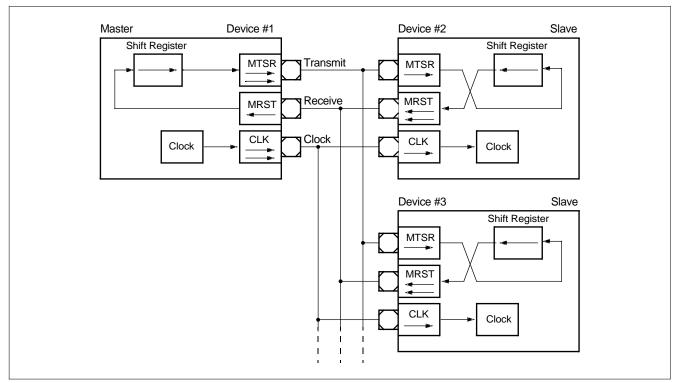

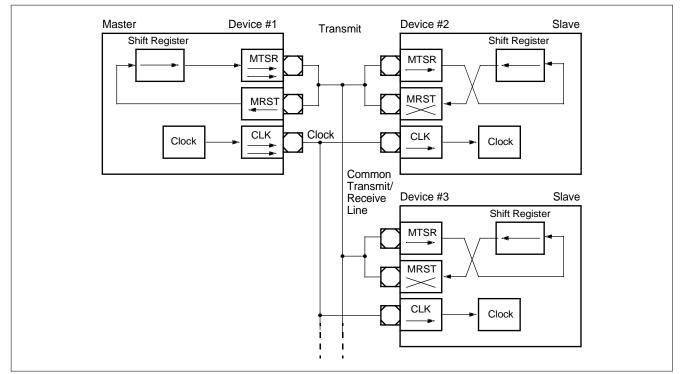

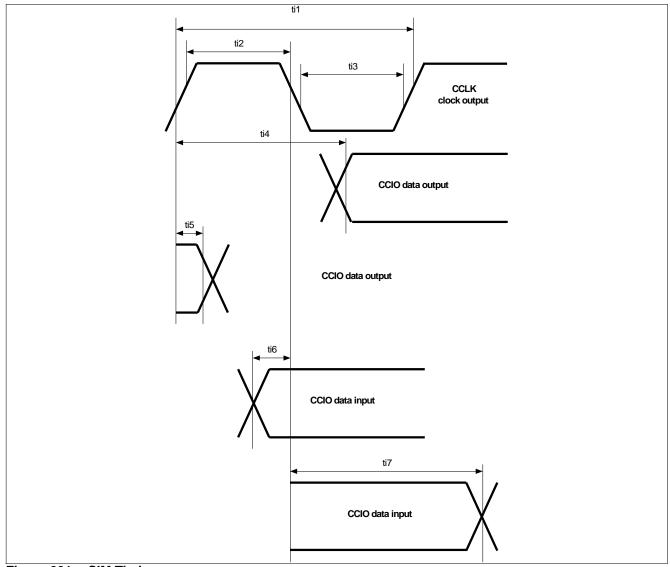

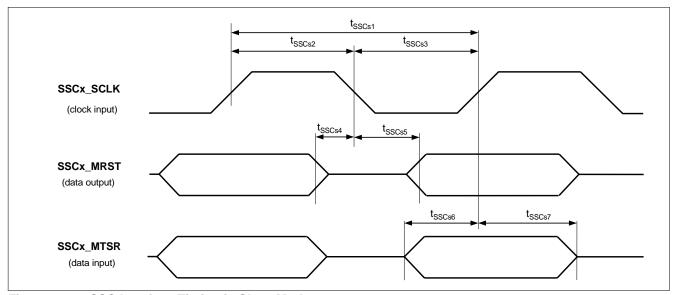

| Figure 101 | SSC Interface Diagram                                   | 285   |

|------------|---------------------------------------------------------|-------|

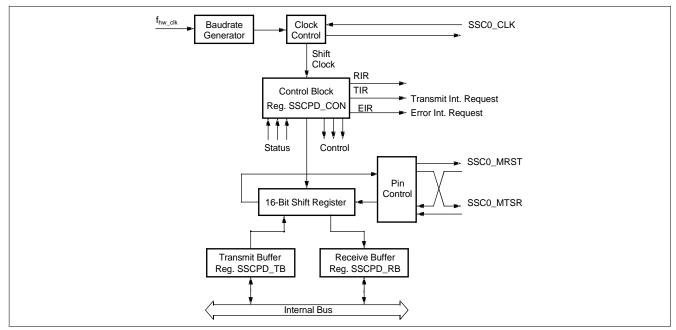

| Figure 102 | Synchronous Serial Channel SSC Block Diagram            | 286   |

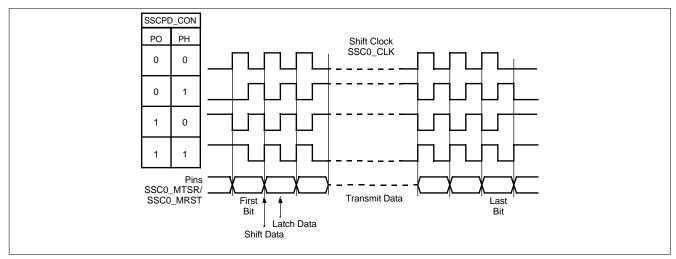

| Figure 103 | Serial Clock Phase and Polarity Options                 | 287   |

| Figure 104 | SSC Duplex Configuration                                | 288   |

| Figure 105 | SSC Half-Duplex Configuration                           | 289   |

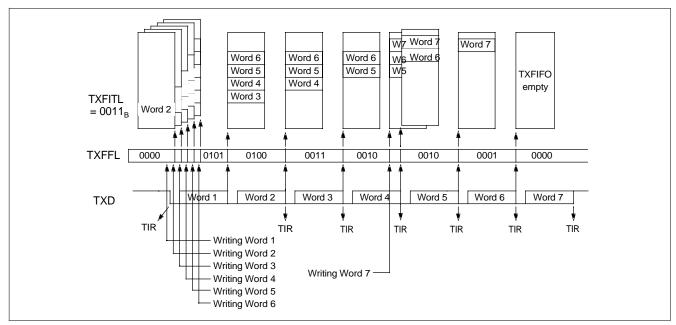

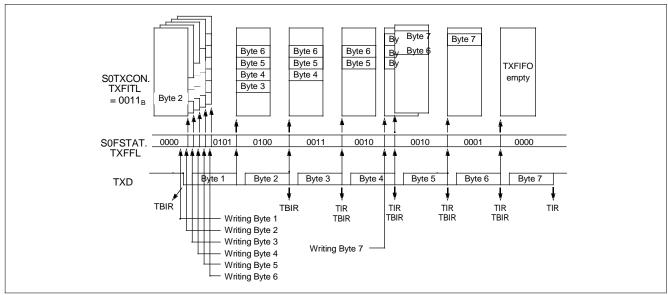

| Figure 106 | Transmit FIFO Operation Example                         | 291   |

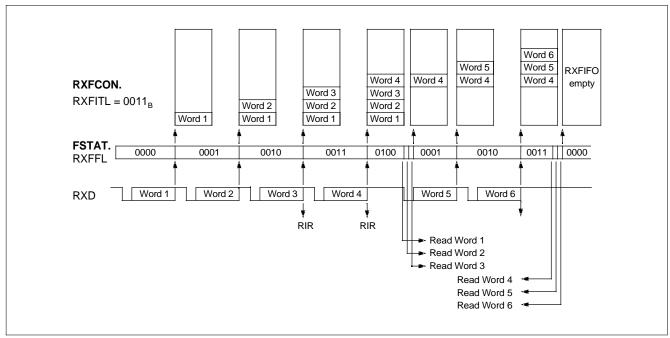

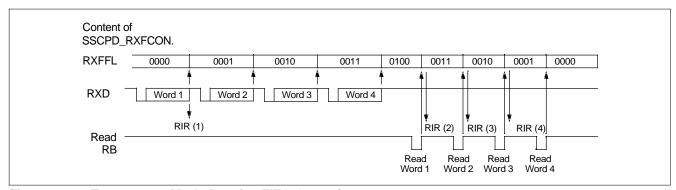

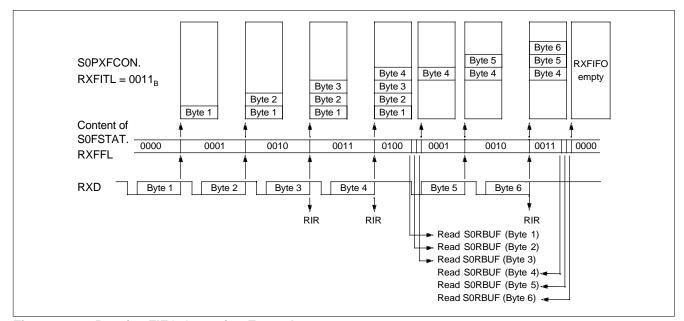

| Figure 107 | Receive FIFO Operation Example                          | 292   |

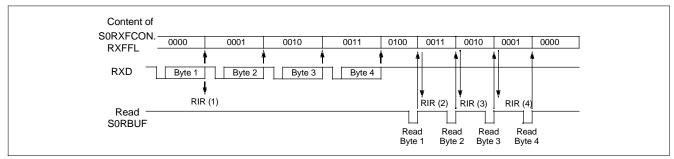

| Figure 108 | Transparent Mode Receive FIFO Operation                 | . 293 |

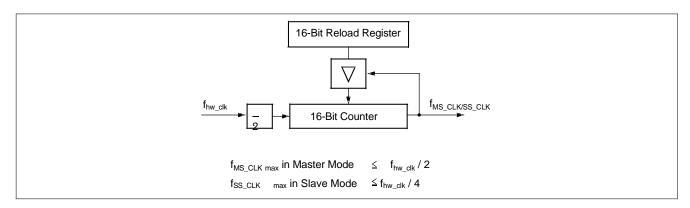

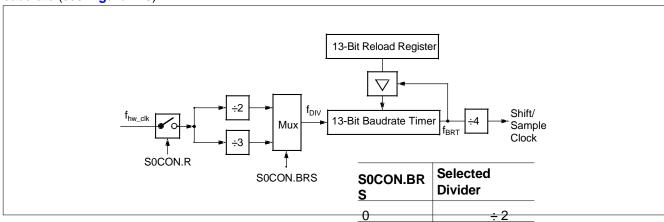

| Figure 109 | SSC Baudrate Generator                                  | 294   |

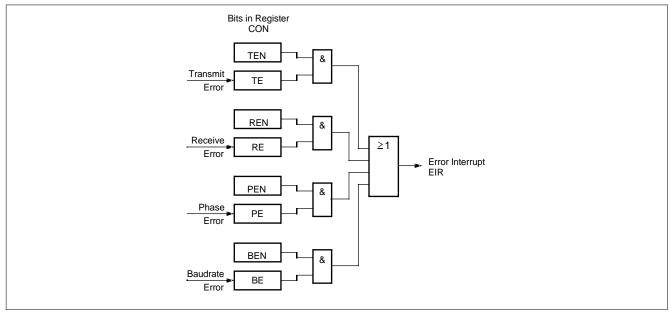

| Figure 110 | SSC Error Interrupt Control                             | 295   |

| Figure 111 | ASC0 Interface Diagram                                  | 307   |

| Figure 112 | Block Diagram of the ASC0                               | 308   |

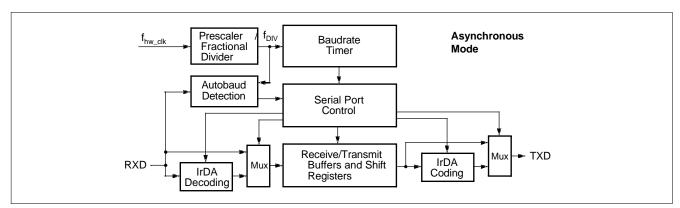

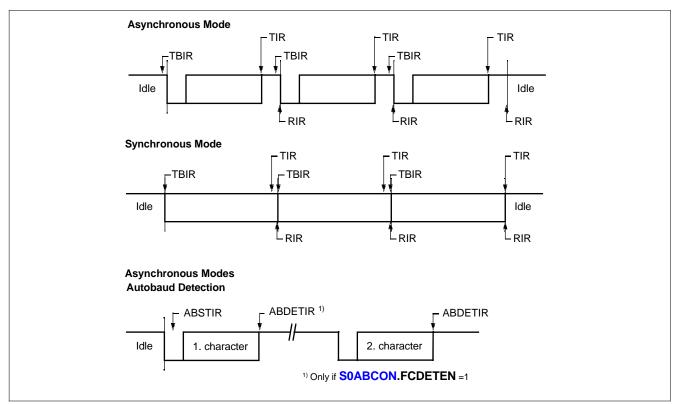

| Figure 113 | Asynchronous Mode of Serial Channel ASC0                |       |

| Figure 114 | Asynchronous 8-Bit Frames                               | 311   |

| Figure 115 | Asynchronous 9-Bit Frames                               |       |

| Figure 116 | IrDA Frame Encoding/Decoding                            | 312   |

| Figure 117 | Transmit FIFO Operation Example                         | 313   |

| Figure 118 | Receive FIFO Operation Example                          |       |

| Figure 119 | Transparent Mode Receive FIFO Operation                 | . 316 |

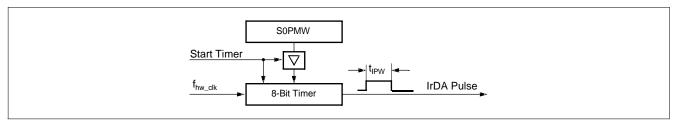

| Figure 120 | Fixed IrDA Pulse Generation                             |       |

| Figure 121 | RXD/TXD Data Path in Asynchronous Modes                 | 318   |

| Figure 122 | Synchronous Mode of Serial Channel ASC0                 | 319   |

| Figure 123 | ASC0 Synchronous Mode Waveforms                         |       |

| Figure 124 | ASC0 Baudrate Generator Circuitry in Asynchronous Modes | 322   |

| Figure 125 | ASC0 Baudrate Generator Circuitry in Synchronous Mode   | 324   |

| Figure 126 | Asynchronous Mode Block Diagram                         | 325   |

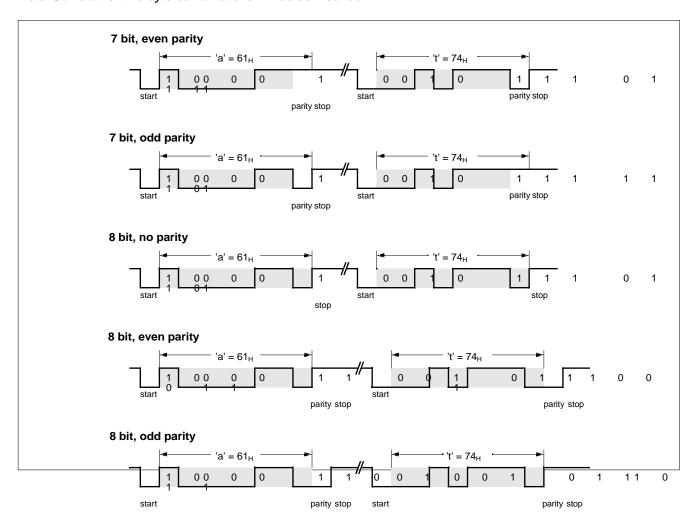

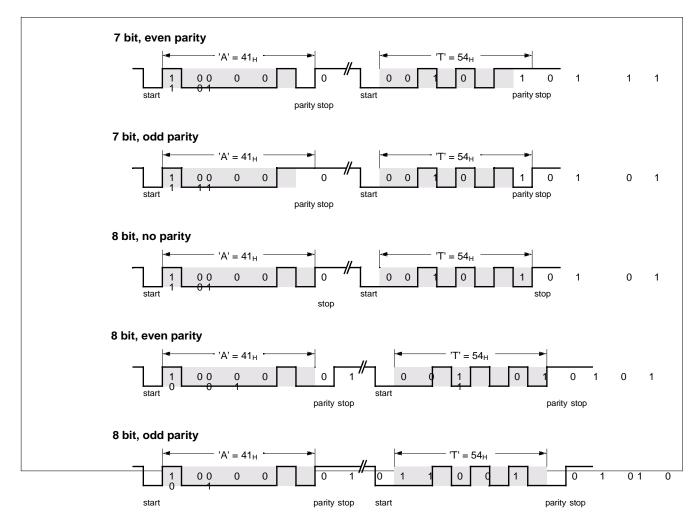

| Figure 127 | Two-Byte Serial Frames with ASCII 'at'                  | 326   |

| Figure 128 | Two-Byte Serial Frames with ASCII 'AT'                  | 327   |

| Figure 129 | ASC0 Interrupt Generation                               | 333   |

| Figure 130 | CAPCOM 1 Interface Diagram                              |       |

| Figure 131 | CAPCOM 2 Interface Diagram                              | 349   |

| Figure 132 | CAPCOM Unit 1 Block Diagram                             |       |

| Figure 133 | Block Diagram of Timers                                 |       |

| Figure 134 | Capture Mode Block Diagram                              | 354   |

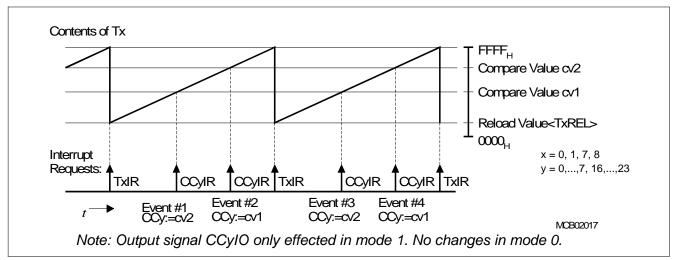

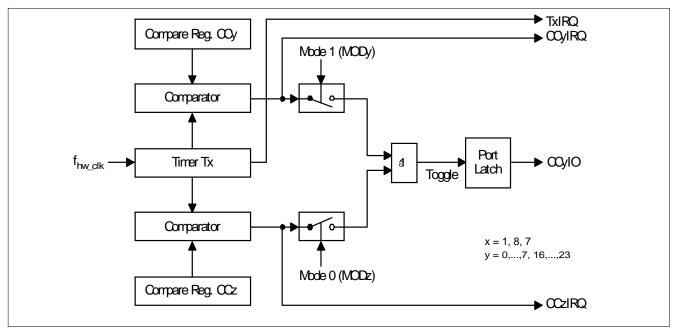

| Figure 135 | Compare Mode 0 and 1 Block Diagram                      | 355   |

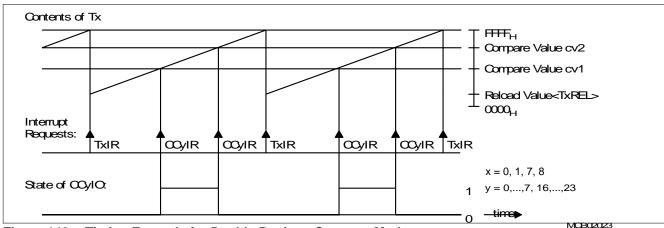

| Figure 136 | Timing Example for Compare Modes 0 and 1                | 355   |

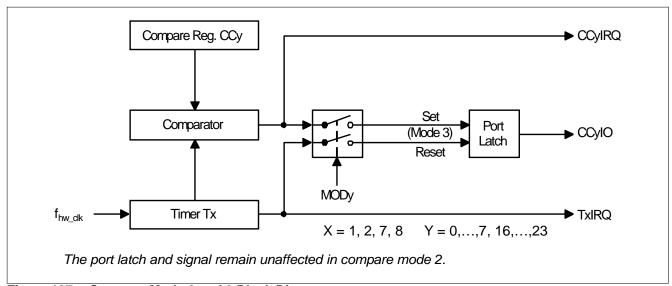

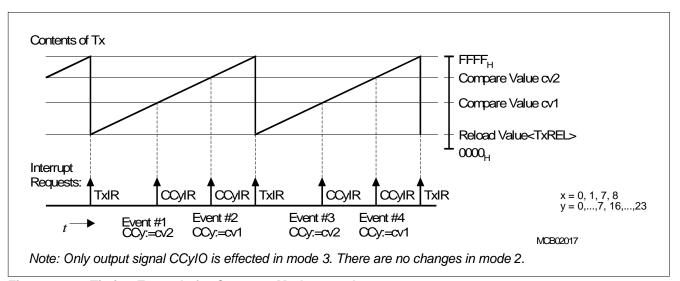

| Figure 137 | Compare Mode 2 and 3 Block Diagram                      | 356   |

| Figure 138 | Timing Example for Compare Modes 2 and 3                | 357   |

| Figure 139 | Double-Register Compare Mode Block Diagram              | 359   |

| Figure 140 | Timing Example for Double-Register Compare Mode         |       |

| Figure 141 | Interface Diagram for Alternative Implementation        | 360   |

| Figure 142 | Port Input Selection for Capture Channels               | 369   |

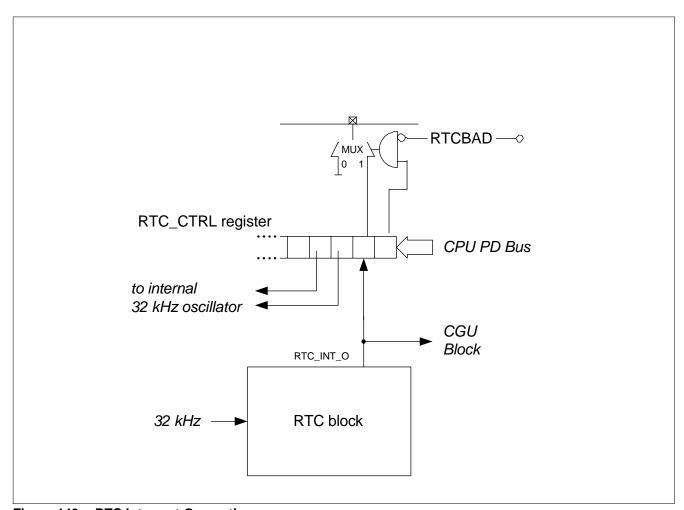

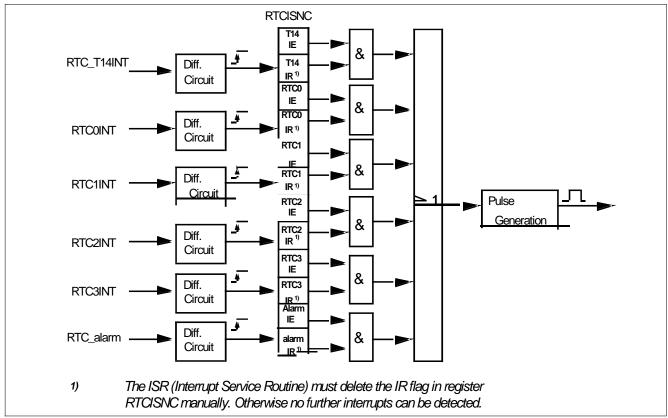

| Figure 143 | RTC Interrupt Generation                                | 379   |

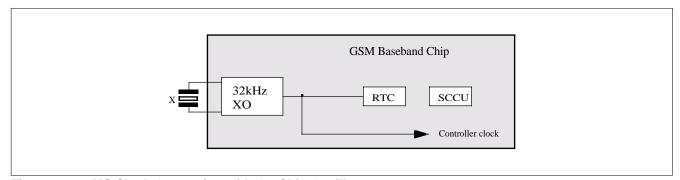

| Figure 144 | MS Clock Generation with On-Chip Oscillators            |       |

| Figure 145 | Circuitry to Use the Internal 32 kHz Oscillator         | 381   |

| Figure 146 | Circuitry to Use the External 32 kHz Oscillator         | 382   |

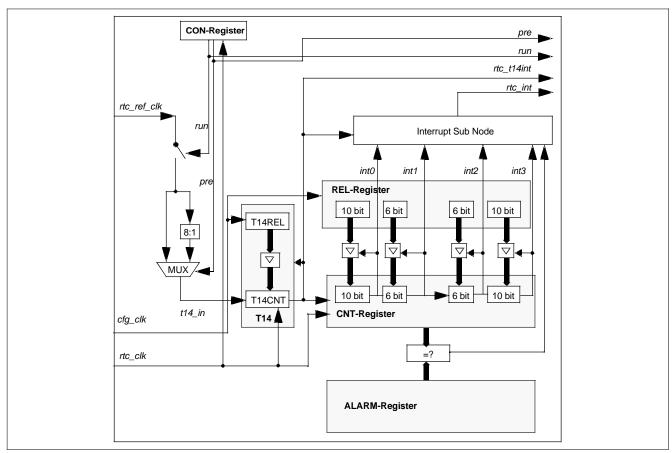

| Figure 147 | RTC Kernel Block Diagram                                | 383   |

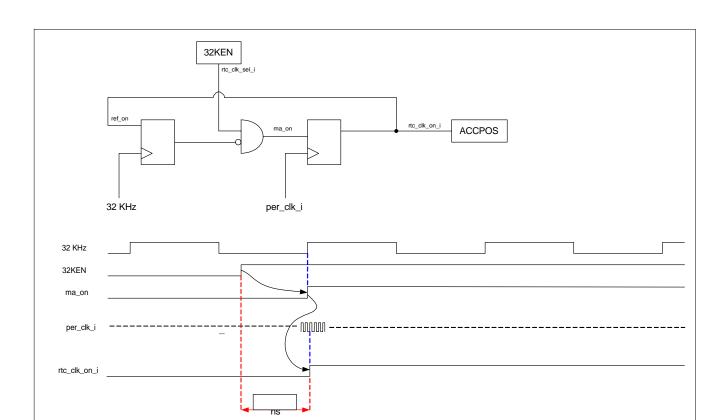

| Figure 148 | ACCPOS Bit Generation.                                  | 385   |

| Figure 149 | Differentiating Circuits for RTC interrupt              | 389   |

| Figure 150 | GPT12 Interface Diagram                                 | 393   |

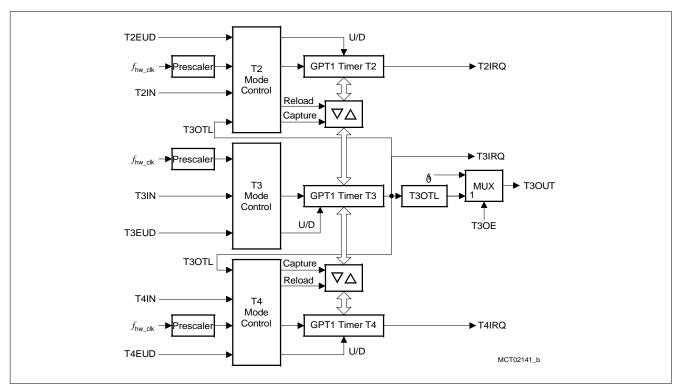

| Figure 151 | Structure of Timer Block 1                              | 301   |

| CONFIDENTIAL | List of Figures |

|--------------|-----------------|

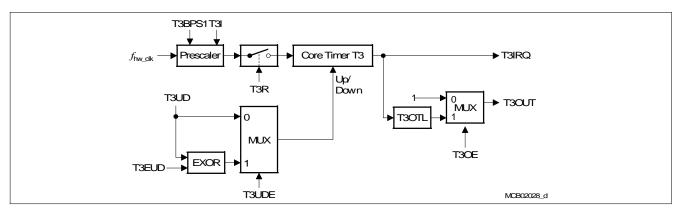

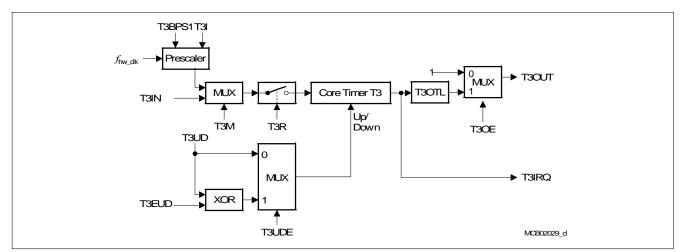

| Figure 152 | Block Diagram of Core Timer T3 in Timer Mode                                            | 396        |

|------------|-----------------------------------------------------------------------------------------|------------|

| Figure 153 | Block Diagram of Core Timer T3 in Gated Timer Mode                                      | 397        |

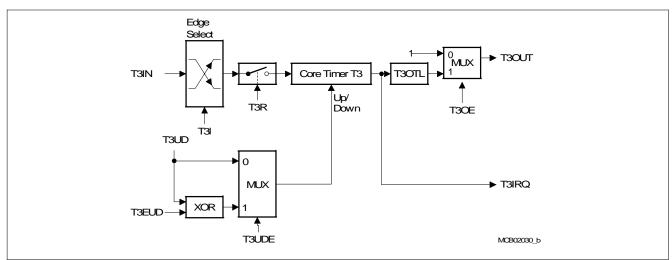

| Figure 154 | Block Diagram of Core Timer T3 in Counter Mode                                          | 397        |

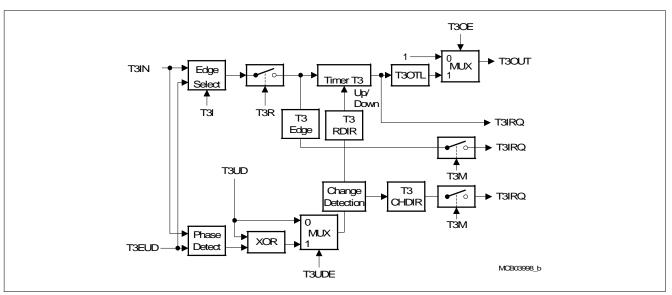

| Figure 155 | Block Diagram of Core Timer T3 in Incremental Interface Mode                            | 398        |

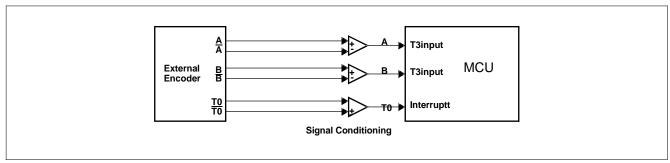

| Figure 156 | Interfacing the Encoder to the Microcontroller                                          | 399        |

| Figure 157 | Evaluation of the Incremental Encoder Signals                                           | 400        |

| Figure 158 | Evaluation of the Incremental Encoder Signals                                           |            |

| Figure 159 | Block Diagram of an Auxiliary Timer in Counter Mode                                     | 401        |

| Figure 160 | Concatenation of Core Timer T3 and an Auxiliary Timer                                   |            |

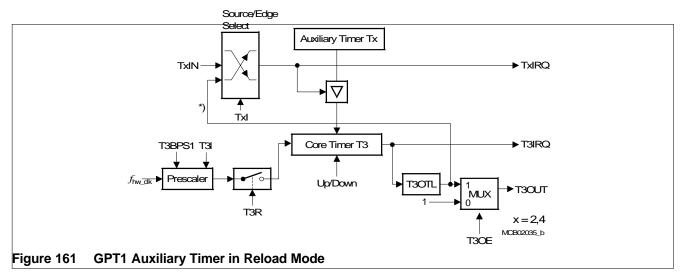

| Figure 161 | GPT1 Auxiliary Timer in Reload Mode                                                     |            |

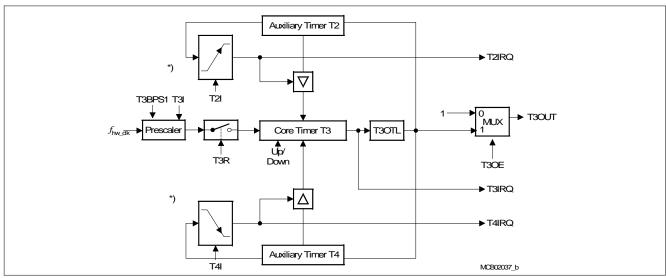

| Figure 162 | GPT1 Timer Reload Configuration for PWM Generation                                      |            |

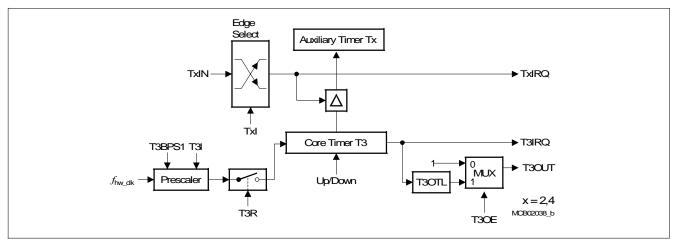

| Figure 163 | Auxiliary Timer of Timer Block 1 in Capture Mode                                        |            |

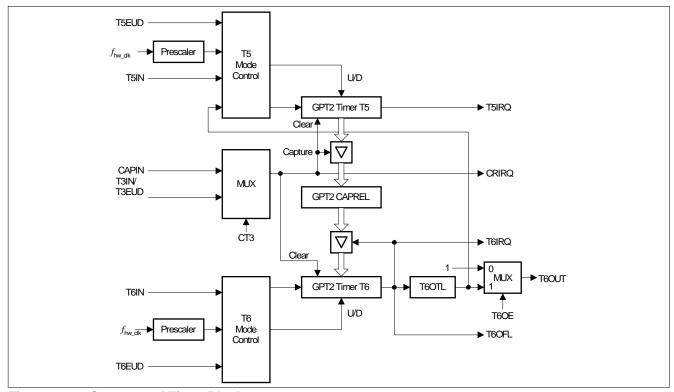

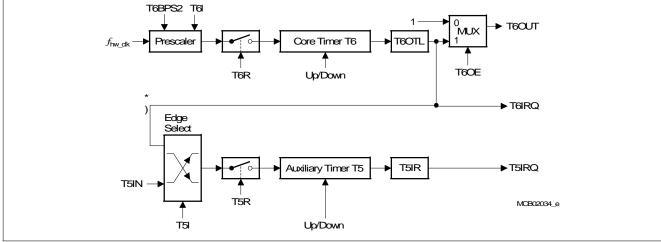

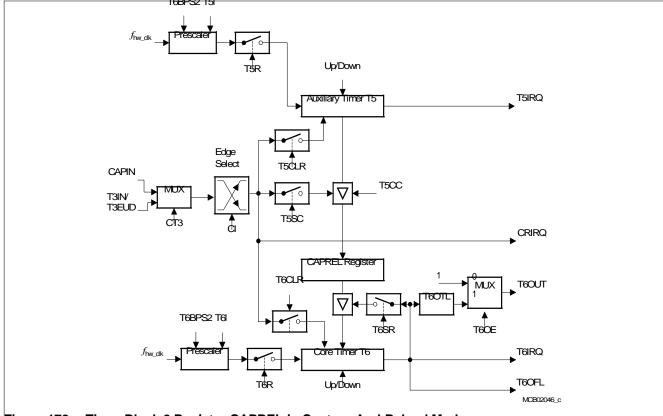

| Figure 164 | Structure of Timer Block 2                                                              |            |

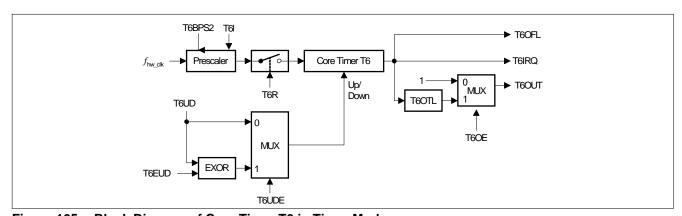

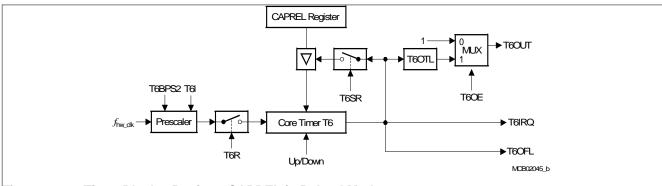

| Figure 165 | Block Diagram of Core Timer T6 in Timer Mode                                            |            |

| Figure 166 | Block Diagram of Core Timer T6 in Gated Timer Mode                                      |            |

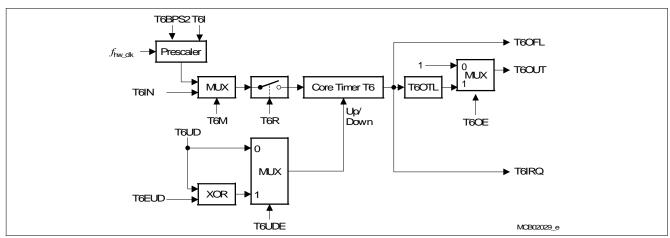

| Figure 167 | Block Diagram of Core Timer T6 in Counter Mode                                          |            |

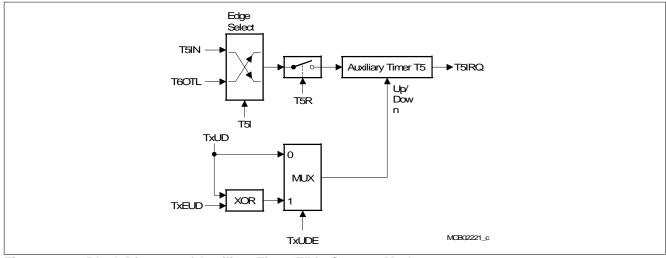

| Figure 168 | Block Diagram of Auxiliary Timer T5 in Counter Mode                                     |            |

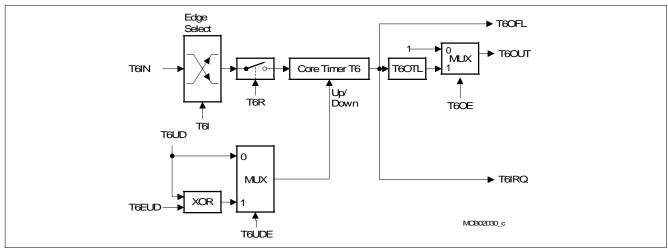

| Figure 169 | Concatenation of Core Timer T6 and Auxiliary Timer T5                                   |            |

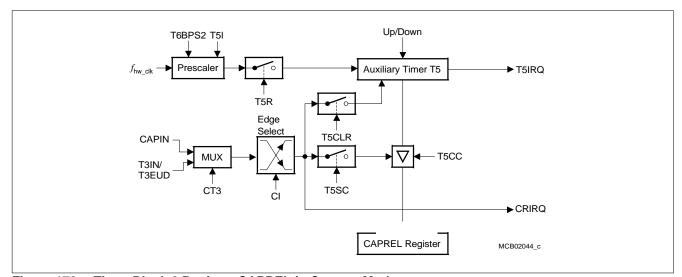

| Figure 170 | Timer Block 2 Register CAPREL in Capture Mode                                           |            |

| Figure 171 | Timer Block 2 Register CAPREL in Reload Mode                                            |            |

| Figure 172 | Timer Block 2 Register CAPREL in Capture-And-Reload Mode                                |            |

| Figure 173 | Architecture of Pad Control and Port Logic                                              |            |

| Figure 174 | Example for Connecting PCL Blocks and Chip Internal Blocks                              |            |

| Figure 175 | Flash Write Protection Functional Diagram                                               |            |

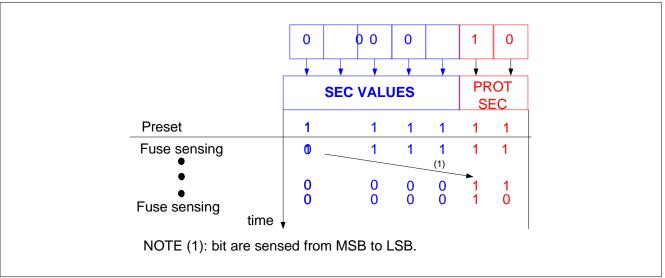

| Figure 176 | Fuse sensing of ID_SNUM5                                                                |            |

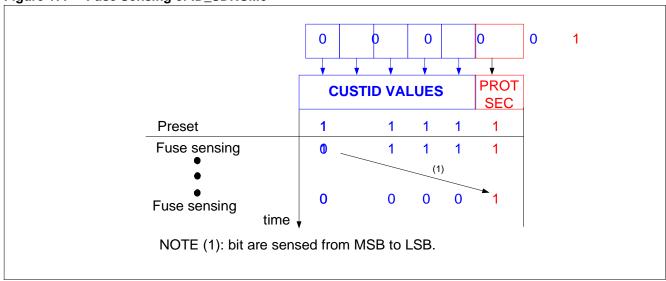

| Figure 177 | Fuse Sensing of ID_SDNUM6                                                               |            |

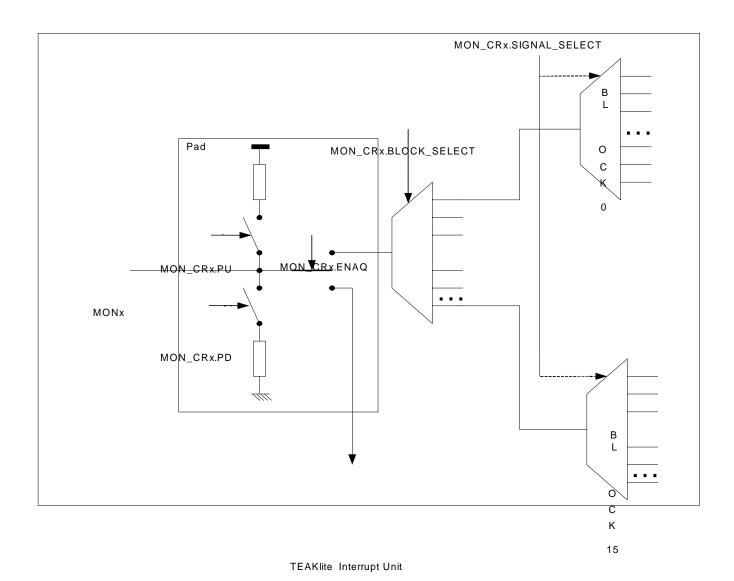

| Figure 178 | Monitoring of Internal Signals at the Monitor Pads                                      |            |

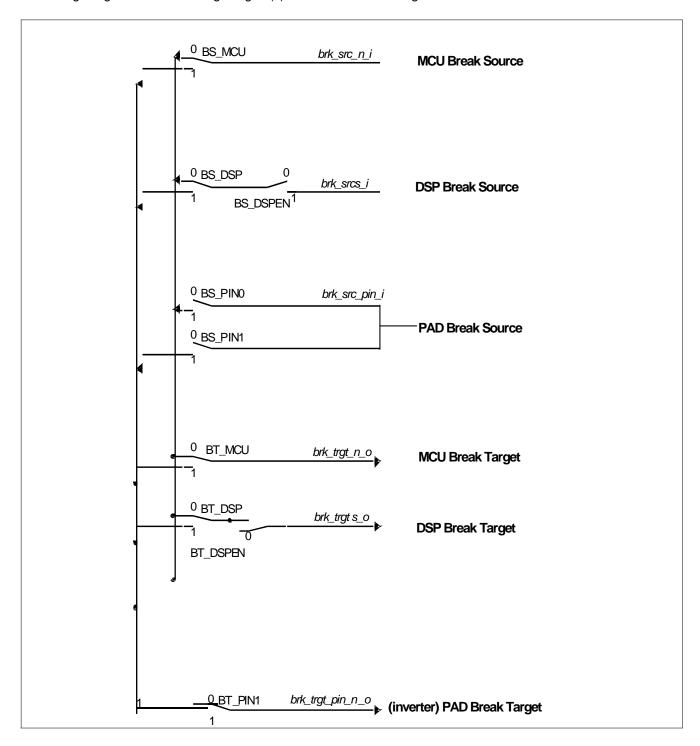

| Figure 179 | Break Switch Interface                                                                  |            |

| Figure 180 | Break Bus Switch                                                                        |            |

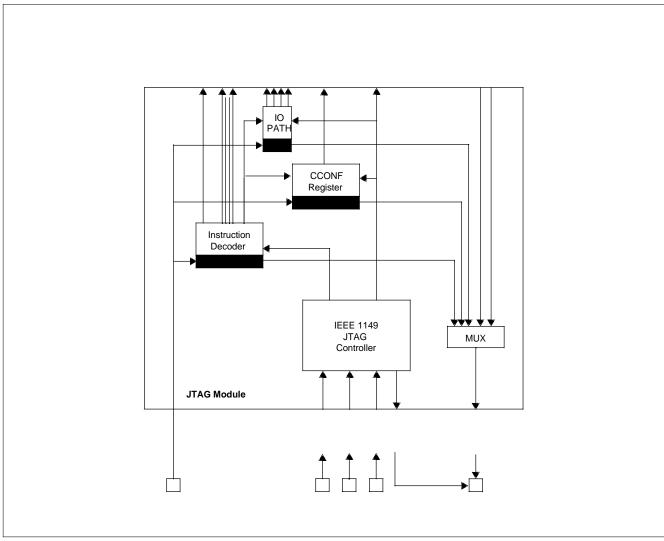

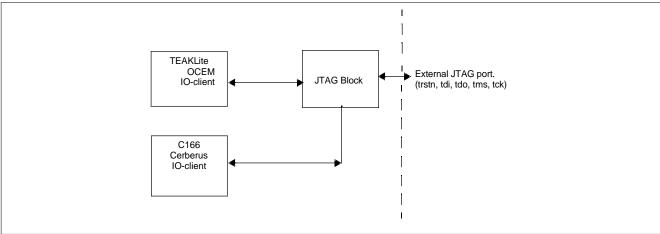

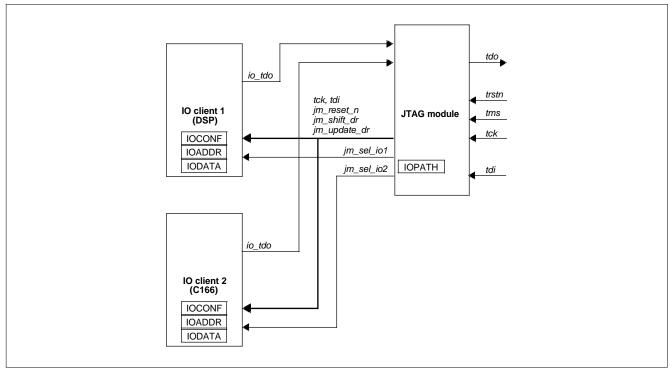

| Figure 181 | JTAG Module Block Diagram                                                               |            |

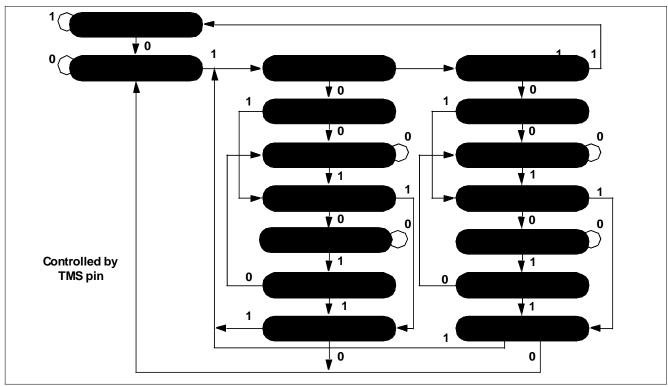

| Figure 182 | TAP Controller State Diagram                                                            |            |

| Figure 183 | IOPATH Register                                                                         |            |

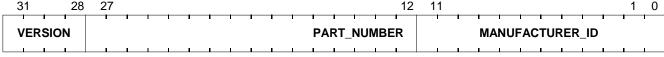

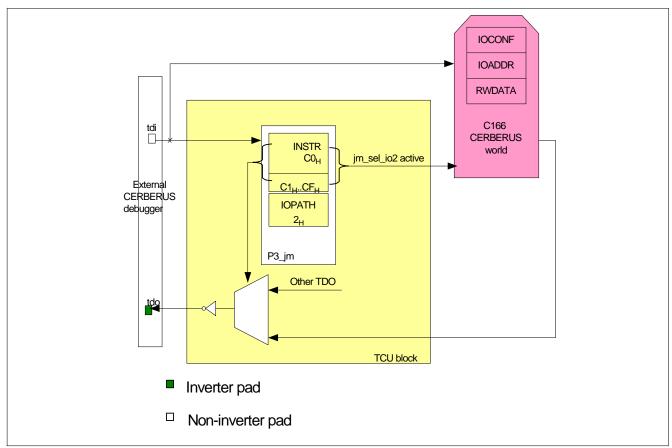

| Figure 184 | JTAG IO Mode Application Example                                                        |            |

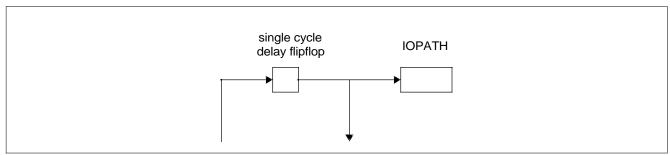

| Figure 185 | IO Mode Basic Architecture                                                              | 477        |

| Figure 186 | C166 CERBERUS IO-Client Selection                                                       | 478        |

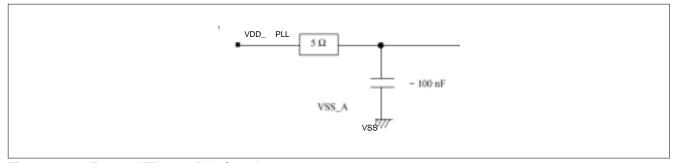

| Figure 187 | External Filter at PLL Supply                                                           |            |

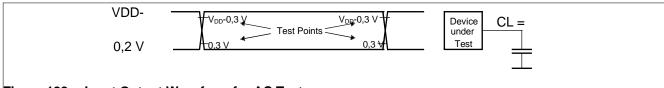

| Figure 188 | Input Output Waveform for AC Test                                                       | 512        |

| Figure 189 | Float Waveforms                                                                         | 512        |

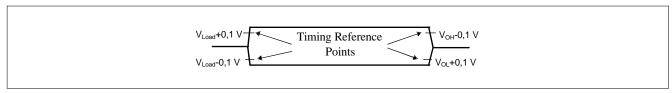

| Figure 190 | Overview of EBU Parameter Characterizations                                             | 520        |

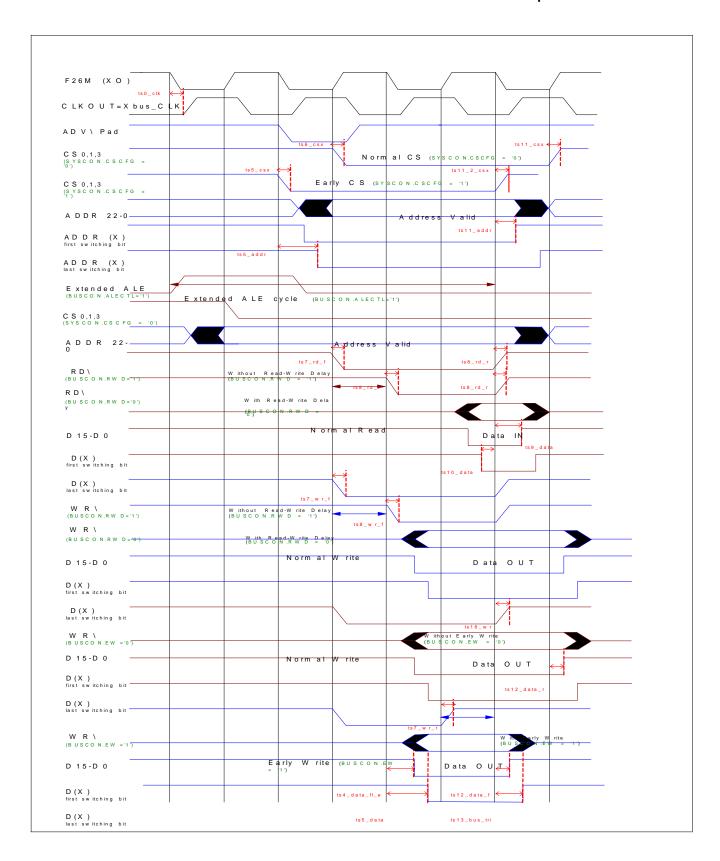

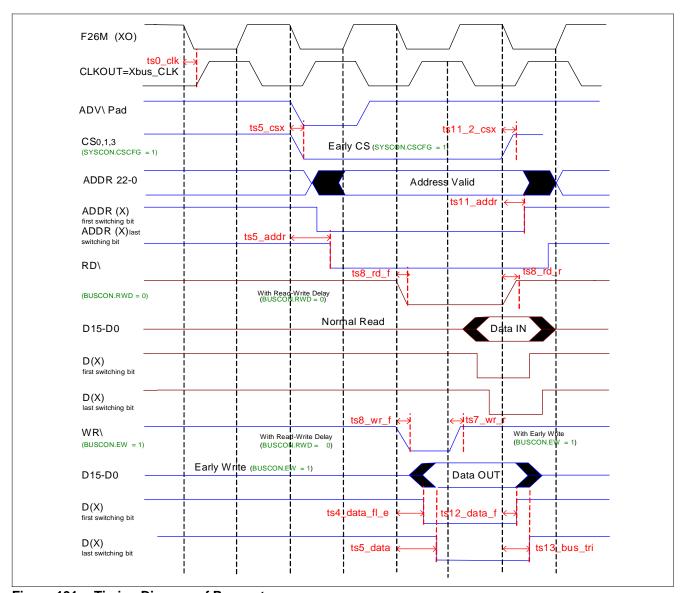

| Figure 191 | Timing Diagram of Parameters                                                            | 521        |

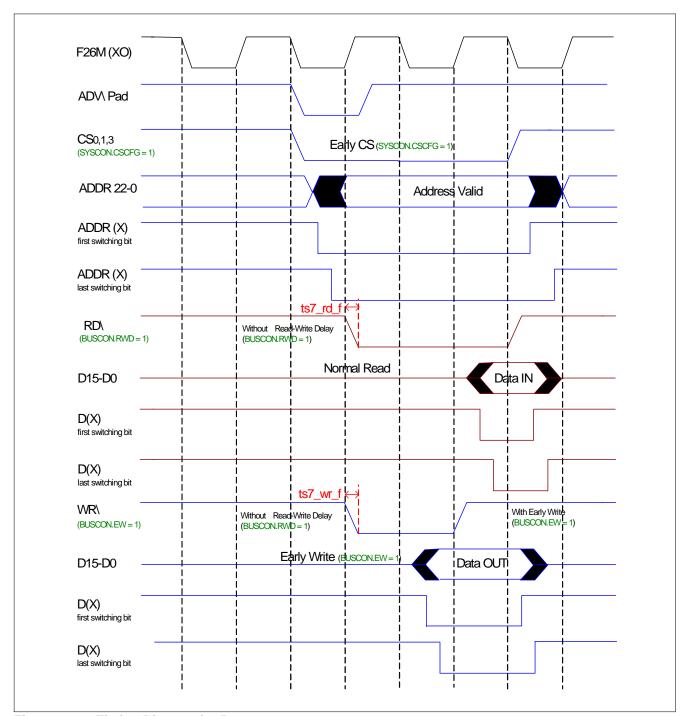

| Figure 192 | Timing Diagram for Parameters                                                           | 522        |

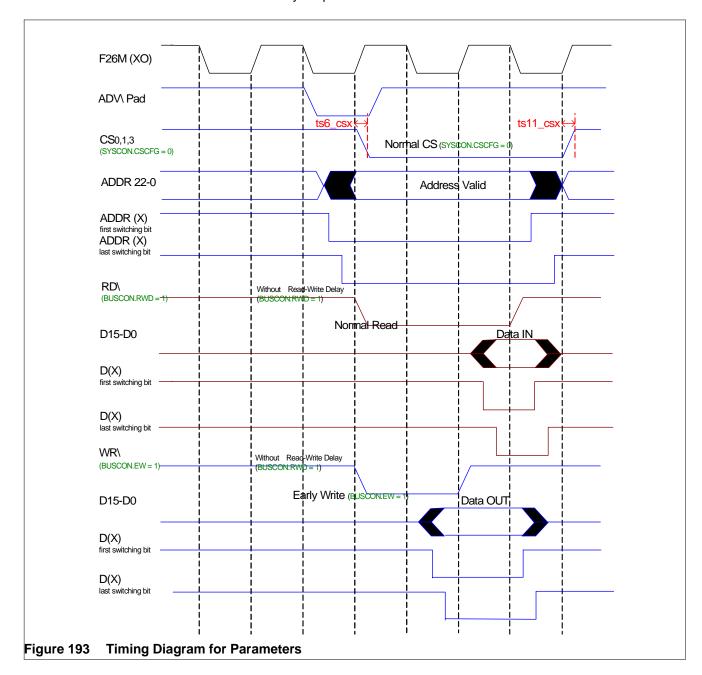

| Figure 193 | Timing Diagram for Parameters                                                           | 523        |

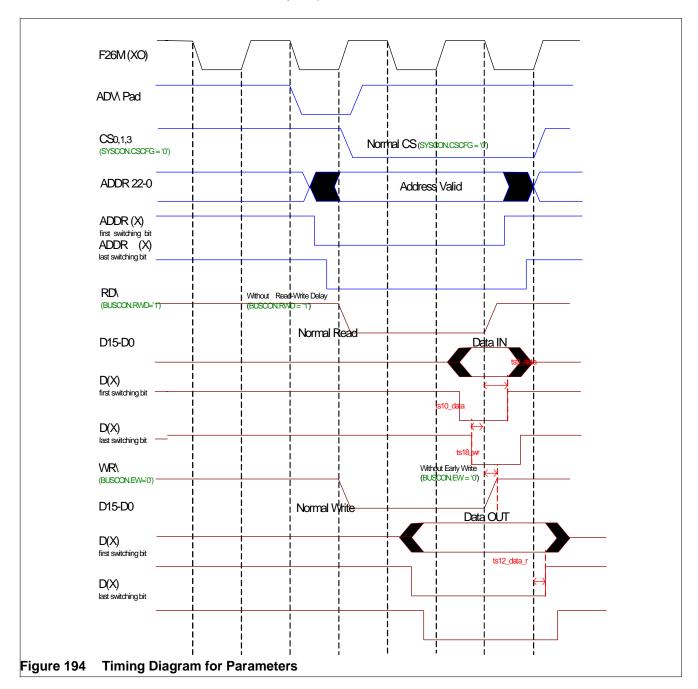

| Figure 194 | Timing Diagram for Parameters                                                           | 524        |

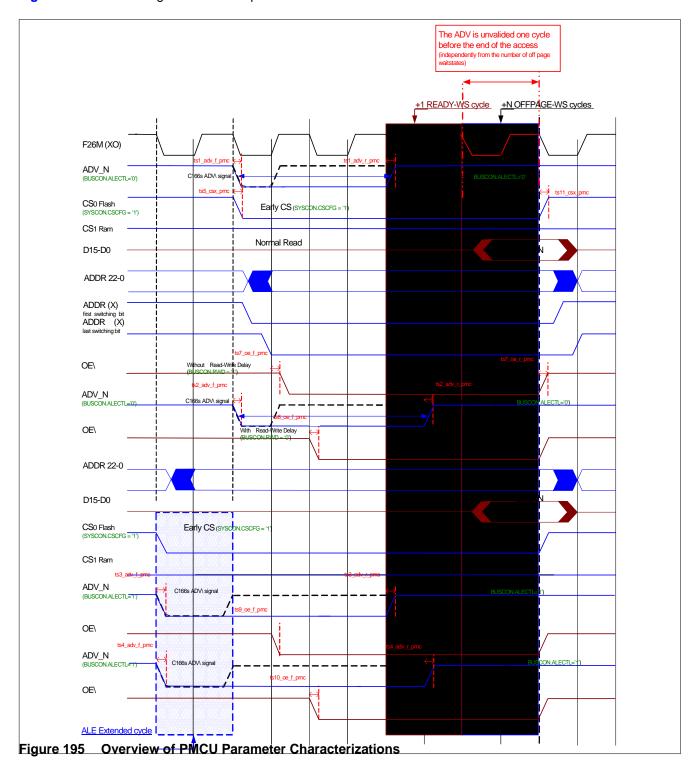

| Figure 195 | Overview of PMCU Parameter Characterizations                                            |            |

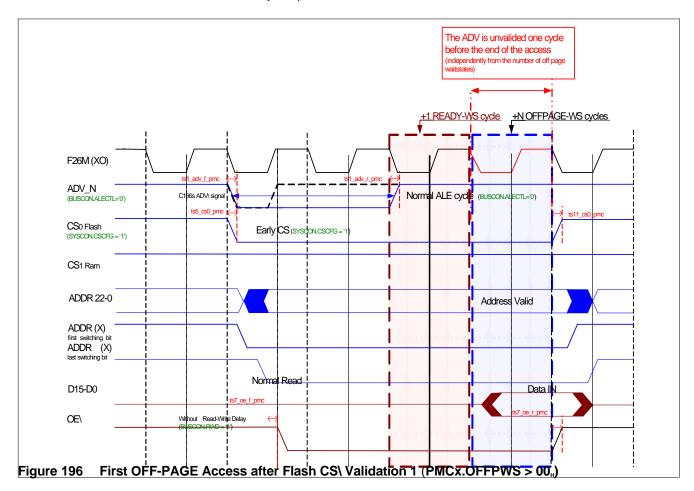

| Figure 196 | First OFF-PAGE Access after Flash CS\ Validation 1 (PMCx.OFFPWS > 00 <sub>H</sub> )     |            |

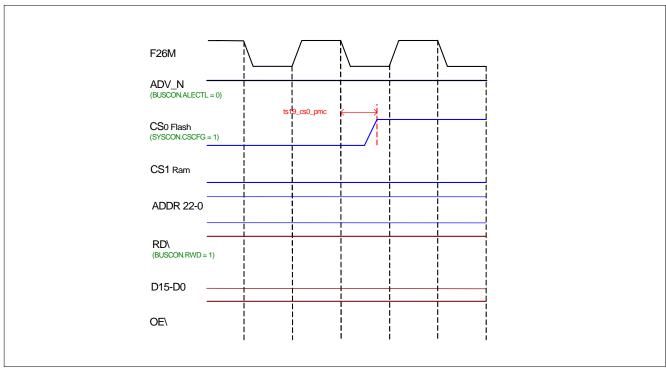

| Figure 197 | Switch of CS\ from Valid to Invalid (When Timeout of PMC_TIMER is Reached)              | 527        |

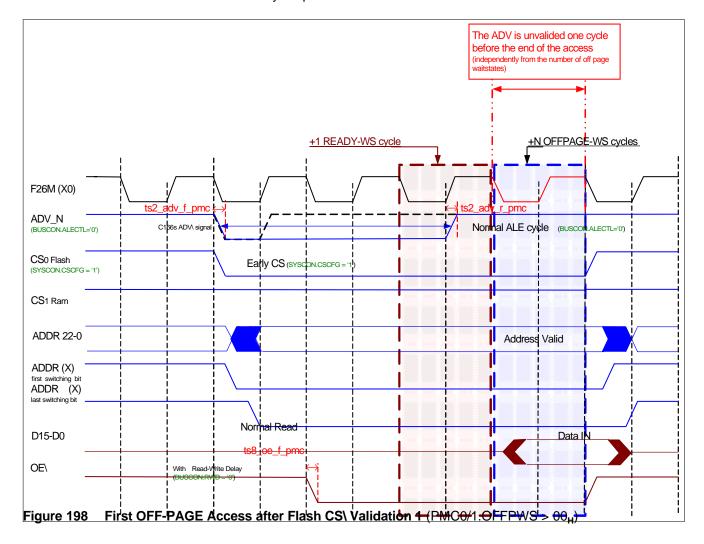

| Figure 198 | First OFF-PAGE Access after Flash CS\ Validation 1 (PMC0/1.OFFPWS > 00 <sub>H</sub> )   |            |

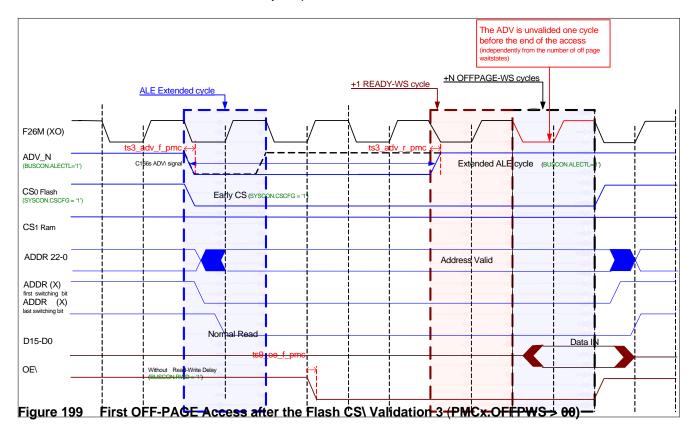

| Figure 199 | First OFF-PAGE Access after the Flash CS\ Validation 3 (PMCx.OFFPWS > 00)               |            |

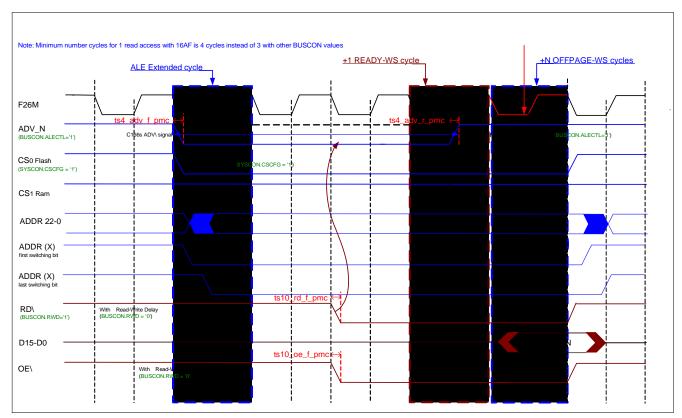

| Figure 200 | First OFF-PAGE Access after the Flash CS\ Validation 5 (PMCx.OFFPWS > 00 <sub>H</sub> ) |            |

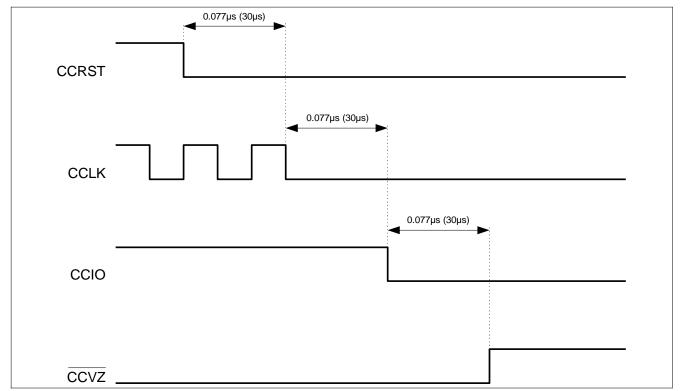

| Figure 201 | SIM Timing                                                                              | 531<br>532 |

| CONFIDENT  | TIAL List of Fig.                                                               | gures |

|------------|---------------------------------------------------------------------------------|-------|

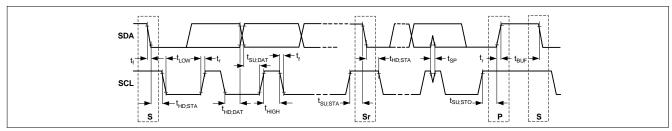

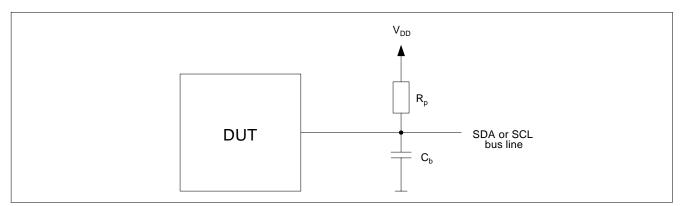

| Figure 203 | Test circuitry of I2C-bus                                                       | 533   |

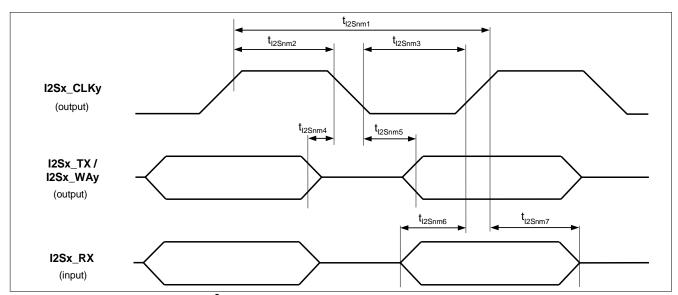

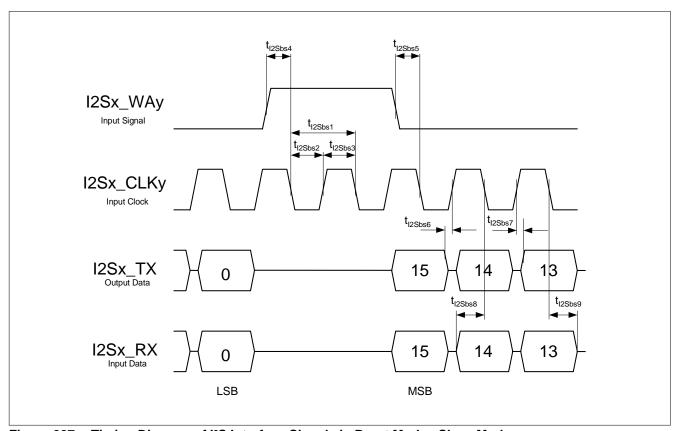

| Figure 204 | Timing Diagram of I <sup>2</sup> S Signals in Normal Mode - Master Mode         | 533   |

| Figure 205 | Timing Diagram of I <sup>2</sup> S Signals in Normal Mode - Slave Mode          | . 534 |

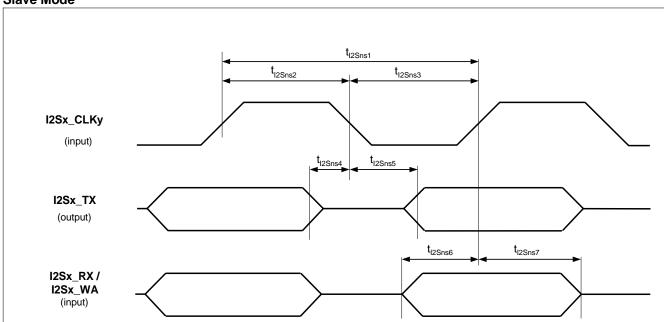

| Figure 206 | Timing Diagram of I <sup>2</sup> S Signals in Burst Mode - Master Mode          | . 535 |

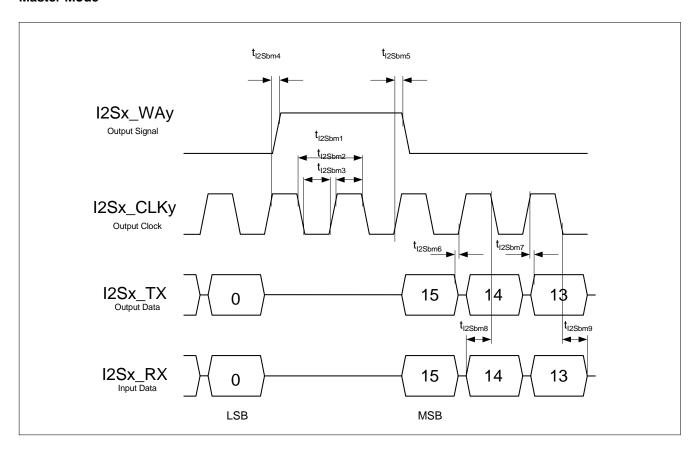

| Figure 207 | Timing Diagram of I <sup>2</sup> S Interface Signals in Burst Mode - Slave Mode | . 536 |

| Figure 208 | Timing Diagram of I <sup>2</sup> S Interface Signals in DAI Mode                | . 537 |

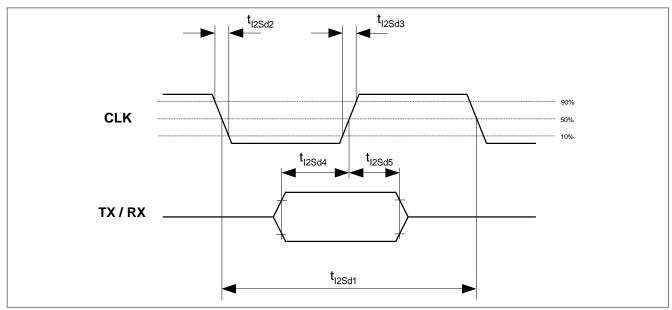

| Figure 209 | Timing of ASC in Synchronous Mode                                               |       |

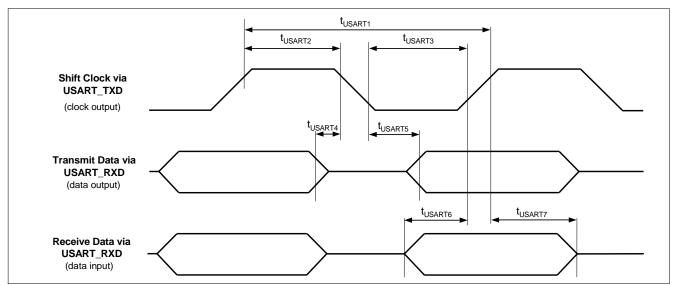

| Figure 210 | SSC Interface Timing in Master Mode                                             |       |

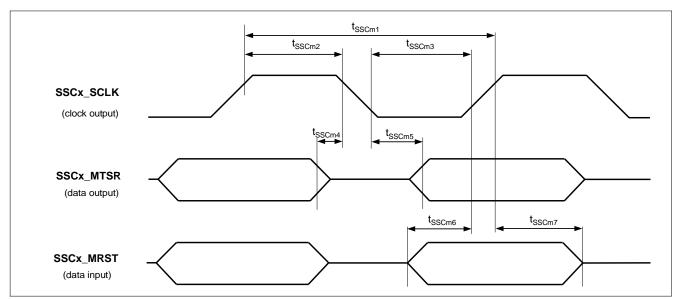

| Figure 211 | SSC Interface Timing in Slave Mode                                              |       |

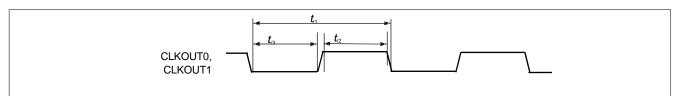

| Figure 212 | Output Clocks: CLKOUT Timing                                                    | 542   |

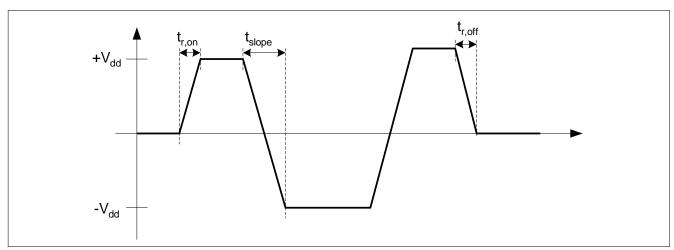

| Figure 213 | Timing Diagram for Analog Ringer Mode                                           |       |

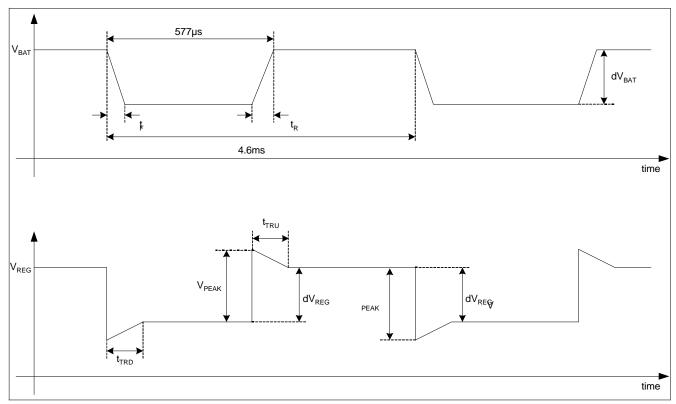

| Figure 214 | Voltage Pattern for Line Regulation and Transient Line Regulation               | . 576 |

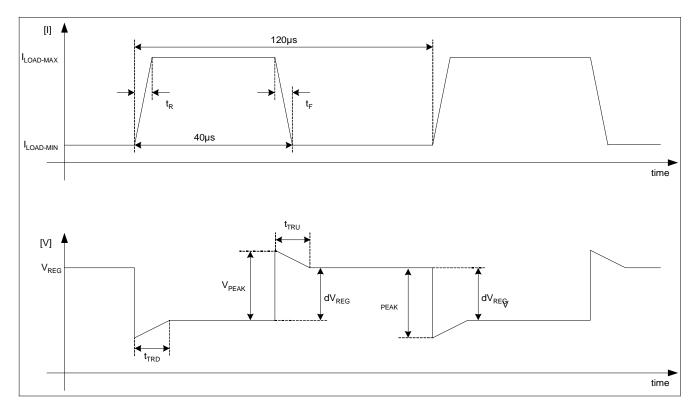

| Figure 215 | Current Pattern for Load Regulation and Transient Load Regulation               | . 577 |

| Figure 216 | Reset Timing Diagram                                                            |       |

| Figure 217 | Reset Interaction Timing Diagram Example                                        | . 584 |

| Figure 218 | Boot Configuration Latch Register                                               |       |

| Figure 219 | Break Switch Interface                                                          |       |

| Figure 220 | JTAG IO Mode Application Example                                                |       |

## CONFIDENTIAL List of Tables

# **List of Tables**

| Table 1  | E-GOLDvoice Version Naming                                |      |

|----------|-----------------------------------------------------------|------|

| Table 2  | Legend for Figure 3                                       | 27   |

| Table 3  | Pin Descriptions                                          | 32   |

| Table 4  | Pin Definition and Function                               | . 52 |

| Table 5  | Target Operating Frequencies for E-GOLDvoice              | 65   |

| Table 6  | MCU Clock Master                                          | 69   |

| Table 7  | MCU Sub-System Clock                                      | 69   |

| Table 8  | MCU Sub-System Bus Clocks                                 | . 69 |

| Table 9  | MCU Sub-System Peripheral Clocks (ASC0, SSC, PCL, IIC)    | . 70 |

| Table 10 | MCU Sub-System Peripheral Clocks (CAPCOM, GPT)            |      |

| Table 11 | DSP Clock Sources                                         | . 72 |

| Table 12 | Analog Clock Generation                                   | 74   |

| Table 13 | The Analog Clocks                                         | 74   |

| Table 14 | Output Clock                                              | 75   |

| Table 15 | Phase Shifter Frequencies                                 | 79   |

| Table 16 | Setup of register SCCUSPCR                                | . 85 |

| Table 17 | SCCU Signal Descriptions                                  | . 90 |

| Table 18 | SCCU Register List 1                                      |      |

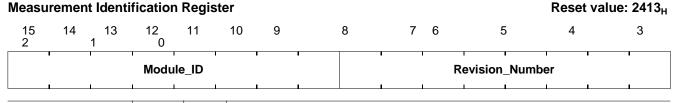

| Table 19 | Measurement Interface Register List                       |      |

| Table 20 | Measurement Switch Settings                               |      |

| Table 21 | General Pre-Amplifier Settings                            | 117  |

| Table 22 | Resistors for Measurement Circuits                        | 117  |

| Table 23 | Measurement BPI Interrupt Requests (Service Requests)     |      |

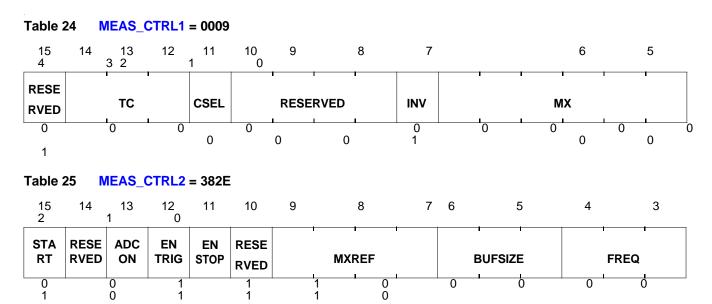

| Table 24 | MEAS_CTRL1 = 0009                                         | 134  |

| Table 25 | MEAS_CTRL2 = 382E                                         | 134  |

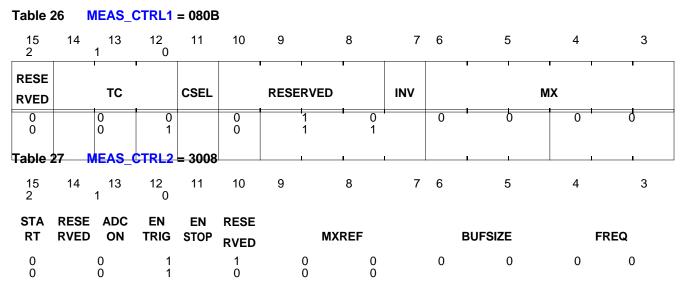

| Table 26 | MEAS_CTRL1 = 080B                                         | 134  |

| Table 27 | MEAS_CTRL2 = 3008                                         | 134  |

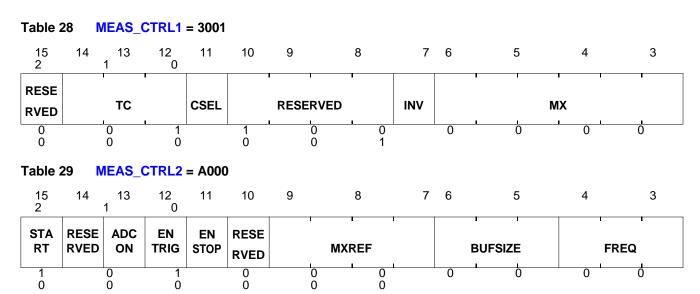

| Table 28 | MEAS_CTRL1 = 3001                                         | 135  |

| Table 29 | MEAS_CTRL2 = A000                                         |      |

| Table 30 | K and L Values for Various Bus Clock Frequencies          |      |

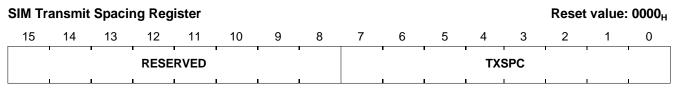

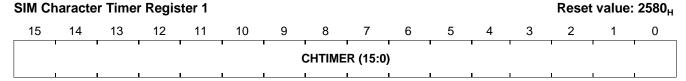

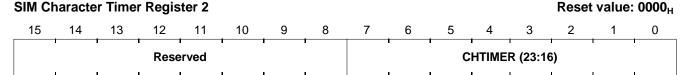

| Table 31 | SIM Register Overview                                     | 146  |

| Table 32 | RF RAM Partitioning of the RF Control Unit (Type 1)       |      |

| Table 33 | RF RAM Partitioning of the RF Control Unit (Type 2)       | 172  |

| Table 34 | Structure of Telegrams                                    | 173  |

| Table 35 | GSM Timer Unit Signals                                    |      |

| Table 36 | Structure of Timing Events                                | 184  |

| Table 37 | Structure of Timing Advance                               | 185  |

| Table 38 | K and L Values for Various Kernel Clock Frequency Errors  | 200  |

| Table 39 | Summary of External Bus Modes                             | 203  |

| Table 40 | Use of WRL#, WRH#, A0, BHE for WRITE                      |      |

| Table 41 | Use of WRL#, WRH#, A0, BHE for READ                       | 208  |

| Table 42 | Bus Mode Versus Performance                               | 208  |

| Table 43 | Chip-Select Generation Modes                              | 209  |

| Table 44 | Address Window Definition                                 | 217  |

| Table 45 | Internal Generated Supply Voltages by LDOs                |      |

| Table 46 | PMU Registers                                             | 235  |

| Table 47 | Tristate Function of the Baseband                         | 243  |

| Table 48 | Turn-On sequence of Power Supply Functions                | 247  |

| Table 49 | Min/Typ/Max Startup time from VBAT rise to Baseband reset | 248  |

|          |                                                           |      |

| CONFIDENTIAL | List of Table |

|--------------|---------------|

|              |               |

| Table 50  | Control Function of VCXOEN                                                                      | 250 |

|-----------|-------------------------------------------------------------------------------------------------|-----|

| Table 51  | Control Function of the Regulators                                                              |     |

| Table 52  | Default setting of the LDOs                                                                     |     |

| Table 53  | Power Loss Examples for the BC807 in a SOT-23 Package                                           |     |

| Table 54  | Peak Current through the LED's for different reference voltage settings and shunt resistances . |     |

| Table 55  | PMU Registers                                                                                   | 260 |

| Table 56  | I2C Register List                                                                               |     |

| Table 57  | IIC-Bus Baud Rate Selection for BRPMOD = 0                                                      |     |

| Table 58  | IIC-Bus Baud Rate Selection for BRPMOD = 1                                                      |     |

| Table 59  | Interrupt Sources                                                                               |     |

| Table 60  | Typical Baudrates of the SSC (fhw_clk = 52 MHz)                                                 |     |

| Table 61  | SSC Register Summary                                                                            |     |

| Table 62  | SSC Interrupt Sources                                                                           |     |

| Table 63  | Formulas for IrDA Pulse Width Calculation                                                       |     |

| Table 64  | IrDA Pulse Width Adaption to 1.627 ms                                                           |     |

| Table 65  | Asynchronous Baudrate Formulas using Fixed Input Clock Dividers                                 |     |

| Table 66  | Typical Asynchronous Baudrates Using Fixed Input Clock Dividers                                 |     |

| Table 67  | Asynchronous Baudrate Formulas using the Fractional Input Clock Divider                         |     |

| Table 68  | Typical Asynchronous Baudrates using the Fractional Input Clock Divider                         |     |

| Table 69  | Synchronous Baudrate Formulas                                                                   |     |

| Table 70  | Autobaud Detection using Standard Baudrates (fDIV = 11.0592 MHz)                                |     |

| Table 71  | Standard Baudrates - Deviations and Errors for Autobaud Detection                               |     |

| Table 72  | Autobaud Detection using Non-Standard Baudrates (fDIV = 9.6 MHz)                                |     |

| Table 73  | Autobaud Detection Overwrite Values for the CON Register                                        |     |

| Table 74  | ASC0 Register Summary                                                                           |     |

| Table 75  | Timing Examples                                                                                 |     |

| Table 76  | Register Pairs for Double-Register Compare Mode                                                 |     |

| Table 77  | CAPCOM Register Summary                                                                         |     |

| Table 78  | Selection of Capture Modes and Compare Modes                                                    |     |

| Table 79  | CAPCOM 1 Input Signal Selection                                                                 |     |

| Table 80  | CAPCOM 2 Input Signal Selection                                                                 |     |

| Table 81  | CAPCOM Interrupt Sources                                                                        |     |

| Table 82  | RTC Register List                                                                               |     |

| Table 83  | Register Assignment to Clock and Reset Domains                                                  |     |

| Table 84  | Impact on Counting Accuracy                                                                     | 391 |

| Table 85  | Core Timer T3 Count Direction Control                                                           |     |

| Table 86  | Timer 3 Input Parameter Selection: Timer Mode and Gated Timer Mode (all bits in T3CON)          |     |

| Table 87  | Example for Timer 3 Frequencies and Resolutions                                                 |     |

| Table 88  | Core Timer T3 (Counter Mode) Input Edge Selection                                               |     |

| Table 89  | Core Timer T3 (Incremental Interface Mode) Input Edge Selection                                 |     |

| Table 90  | Core Timer T3 (Incremental Interface Mode) Count Direction                                      | 399 |

| Table 91  | Timer 2,4 Input Parameter Selection: Timer Mode and Gated Timer Mode                            | 401 |

| Table 92  | Auxiliary Timer (Counter Mode) Input Edge Selection                                             |     |

| Table 93  | Timer x Input Parameter Selection for Incremental Interface Mode                                |     |

| Table 94  | Core Timer T6 Count Direction Control (Tx = T5 or T6)                                           |     |

| Table 95  | Timer 6 Input Parameter Selection: Timer Mode and Gated Timer Mode                              |     |

| Table 96  | Core Timer T6 (Counter Mode) Input Edge Selection                                               |     |

| Table 97  | Timer 5 Input Parameter Selection: Timer Mode and Gated Timer Mode                              |     |

| Table 98  | Auxiliary Timer (Counter Mode) Input Edge Selection                                             |     |

| Table 99  | GPT12 Register Summary                                                                          |     |

| Table 100 | Timer 3 Input Parameter Selection for Timer Mode and Gated Timer Mode                           | 417 |

| CONFIDENTIAL | List of Tables |

|--------------|----------------|

| Table 101 | Timer 3 Input Parameter Selection for Counter Mode                      |     |

|-----------|-------------------------------------------------------------------------|-----|

| Table 102 | Timer 3 Input Parameter Selection for Incremental Interface Mode        | 417 |

| Table 103 | Timer 2,4 Input Parameter Selection for Timer Mode and Gated Timer Mode | 419 |

| Table 104 | Timer 2,4 Input Parameter Selection for Counter Mode                    |     |

| Table 105 | Timer 2,4 Input Parameter Selection for Incremental Interface Mode      | 419 |

| Table 106 | Timer 6 Input Parameter Selection for Timer Mode and Gated Timer Mode   | 421 |

| Table 107 | Timer 6 Input Parameter Selection for Counter Mode                      |     |

| Table 108 | Timer 5 Input Parameter Selection for Timer Mode and Gated Timer Mode   |     |

| Table 109 | Timer 5 Input Parameter Selection for Counter Mode                      |     |

| Table 110 | GPT1_2 Interrupt Sources                                                | 424 |

| Table 111 | GPIO Pad Reset Values                                                   | 428 |

| Table 112 | Input Programming                                                       | 429 |

| Table 113 | Output Programming                                                      |     |

| Table 114 | Pad Function Depending on Programming of PCL_ <pad></pad>               | 430 |

| Table 115 | Block List                                                              |     |

| Table 116 | Signals from the DSP (Mainly Interrupts)                                | 438 |

| Table 117 | Signals from DSP                                                        | 440 |

| Table 118 | Signals from A53 Peripherals                                            | 443 |

| Table 119 | Signals from the CGU                                                    | 446 |

| Table 120 | Pad Signals                                                             | 448 |

| Table 121 | INTR_EXT Signals                                                        | 450 |

| Table 122 | PCL_PER Signals                                                         | 452 |

| Table 123 | MCU_PER Signals                                                         | 455 |

| Table 124 | P3_PMU Signals                                                          |     |

| Table 125 | PMU_SUPER Signals                                                       | 459 |

| Table 126 | Main FSM States                                                         | 463 |

| Table 127 | LDOs FSM States                                                         | 464 |

| Table 128 | Bandgap FSM States                                                      | 464 |

| Table 129 | TCU_SUPER Signals                                                       | 464 |

| Table 130 | JTAG Instructions                                                       | 471 |

| Table 131 | JTAG Module Port Pins                                                   | 473 |

| Table 132 | JTAG Module Register Overview                                           | 473 |

| Table 133 | IOPATH Register                                                         | 474 |

| Table 134 | Bit and Non-Bit Addressable SFR Areas                                   | 481 |

| Table 135 | Bit and Non-Bit Addressable ESFR Areas                                  | 485 |

| Table 136 | Address Mapping of X-Bus Peripherals                                    | 489 |

| Table 137 | Register Overview for XADRS1                                            | 490 |

| Table 138 | Register Overview for XADRS2                                            | 494 |

| Table 139 | Register Overview for XADRS4                                            | 495 |

| Table 140 | CHANNEL1 Register                                                       | 498 |

| Table 141 | CHANNEL2 Register                                                       | 498 |

| Table 142 | RXTX Register                                                           | 499 |

| Table 143 | XO_INIT1 Register                                                       | 500 |

| Table 144 | XO_INIT2 Register                                                       | 501 |

| Table 145 | XO_TUNE Register                                                        | 502 |

| Table 146 | Maximum ESD                                                             | 503 |

| Table 147 | Maximum Temperature                                                     | 503 |

| Table 148 | Maximum Power Supply Voltages                                           | 503 |

| Table 149 | Absolute Maximum Ratings, TAMB = -30°C + 85°C                           | 504 |

| Table 150 | Operating Temperature                                                   | 505 |

| Table 151 | Operating Voltage for Fuse programming                                  | 505 |

| CONFIDENTIAL | List of Tables |

|--------------|----------------|

| CONTIDENTIAL |                |

| Table 152 | Digital Power Supply Currents                                                    |     |

|-----------|----------------------------------------------------------------------------------|-----|

| Table 153 | Analog Power Supply Currents (IDD measured with VDD_ANA = 2.5 V)                 |     |

| Table 154 | Input Capacitances and Resistors                                                 |     |

| Table 155 | External Load Capacitances and Resistors                                         | 507 |

| Table 156 | Pad Output Current                                                               |     |

| Table 157 | Pull-Up/Pull-Down Currents                                                       |     |

| Table 158 | Pad Resistances (1,75 V to 2,75 V)                                               |     |

| Table 159 | EBU and PMCU Measured Parameters                                                 |     |

| Table 160 | EBU and PMCU Derived Parameters                                                  | 517 |

| Table 161 | SIM Timing                                                                       |     |

| Table 162 | Timing Characteristic of I <sup>2</sup> C-Bus Interface                          |     |

| Table 163 | Timing Characteristic of I <sup>2</sup> S in Normal Mode - Master Mode           |     |

| Table 164 | Timing Characteristic of I <sup>2</sup> S in normal mode - slave mode            |     |

| Table 165 | Timing Characteristics of I2S in Burst Mode - Master Mode                        | 535 |

| Table 166 | Timing Characteristics of I2S in Burst Mode - Slave Mode                         |     |

| Table 167 | Timing Characteristics of I2S in DAI Mode                                        | 537 |

| Table 168 | Timing Characteristic of ASC with D Drivers in Synchronous Mode                  | 538 |

| Table 169 | Timing Characteristic of SSC in Master Mode                                      | 539 |

| Table 170 | Timing Characteristic of SSC in Slave Mode                                       | 540 |

| Table 171 | Standby Clock Timings                                                            | 541 |

| Table 172 | Output Clock CLKOUT                                                              | 542 |

| Table 173 | General Electrical Characteristics of Audio Receive Path                         | 543 |

| Table 174 | Characteristics of Audio Rx Path for Headset Driver EPpa1                        | 545 |

| Table 175 | Characteristics of Audio Rx Path for differential Earpiece Drivers EPp1 and EPn1 | 545 |

| Table 176 | Characteristics of Audio Rx Path for Loudspeaker LOUD1, LOUD2                    | 545 |

| Table 177 | Electrical characteristics of Ringer Support                                     | 546 |

| Table 178 | Timing Parameters of Ringer Output                                               | 546 |

| Table 179 | Electrical Characteristics of Audio Transmit Path                                | 546 |

| Table 180 | Electrical Characteristics of Microphone Supply                                  | 547 |

| Table 181 | Baseband Transmit Path (Signal Outputs I/IX, Q/QX) for TXON=0                    | 548 |

| Table 182 | ADC Characteristics                                                              | 548 |

| Table 183 | Specification of pins M0 to M2 and M7 to M10                                     | 548 |

| Table 184 | Specification of PAOUTOF1                                                        |     |

| Table 185 | On Chip Temperature Measurement TIC                                              | 550 |

| Table 186 | Specification of Pin PAOUT1 (TXON = 1)                                           | 552 |

| Table 187 | Specification of Pins PAOUT1 (TXON = 0)                                          | 553 |

| Table 188 | AC/DC Characteristics                                                            | 554 |

| Table 189 | LIO Performance Specification                                                    | 562 |

| Table 190 | LANA Performance Specification                                                   | 563 |

| Table 191 | LRFRX Performance Specification                                                  | 565 |

| Table 192 | LRFTRX Performance Specification                                                 | 566 |

| Table 193 | LRFXO Performance Specification                                                  | 568 |

| Table 194 | LRTC Performance Specification                                                   | 569 |

| Table 195 | LD1 Performance Specification                                                    | 570 |

| Table 196 | LSIM Performance Specification                                                   | 571 |

| Table 197 | LMEM Performance Specification                                                   | 573 |

| Table 198 | LBUF Performance Specification                                                   | 574 |

| Table 199 | Charge Detect Power On                                                           | 578 |

| Table 200 | Over-Voltage Detection                                                           | 578 |

| Table 201 | Charge Switch Driver                                                             | 578 |

| Table 202 | VBAT Power On                                                                    | 578 |

| CONFIDEN    | TIAL                              | List of T | ables |

|-------------|-----------------------------------|-----------|-------|

| Table 203   | Battery Voltage Measurement       |           | 579   |

|             | Backlight Comparator              |           |       |

| Table 205   | Block Reset Actions               |           | 582   |

| Table 206   | Power-Off Output Tristate Control |           | 585   |

| Glossary of | Terms                             |           | 588   |

Introduction

#### 1 Introduction

#### 1.1 Overview of E-GOLDvoice

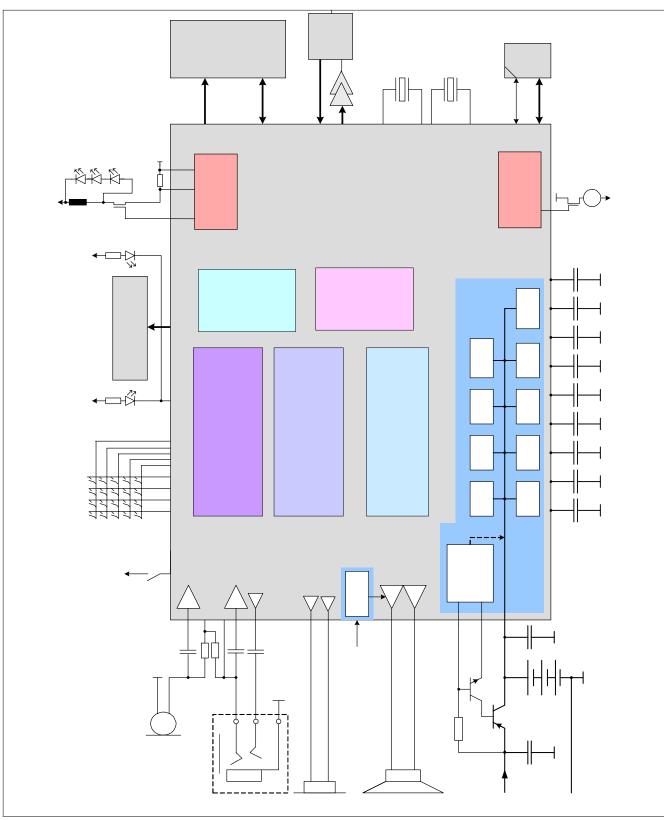

The E-GOLDvoice is a GSM baseband modem including RF transceiver covering the low bands GSM850 / GSM900 and high bands GSM1800 / GSM1900 bands. E-GOLDvoice is Dual Band, therefore, it supports by default a low / high pair of bands at the same time:

- 1. GSM850 / GSM1800

- 2. GSM850 / GSM1900

- 3. GSM900 / GSM1800

- 4. GSM900 / GSM1900.

The E-GOLDvoice is optimized for voice-centric Mobile Phone applications.

The E-GOLDvoice is designed as a single chip solution that integrates the digital, mixed-signal, RF functionality and a direct-to-battery Power Management Unit.

The transceiver consists of:

- Constant gain direct conversion receiver with an analog I/Q baseband interface

- Fully integrated Sigma/Delta-synthesizer capability

- · Fully integrated two-band RF oscillator

- Two-band digital GMSK modulator with digital TX interface

- · Digitally controlled crystal oscillator generating system clocks.

The E-GOLDvoice supports a direct battery connection, hence eliminating the need for an external Power Management Unit. The E-GOLDvoice has different power down modes and an integrated power up sequencer. The E-GOLDvoice is powered by the C166®S MCU and TEAKLite® DSP cores. The operating temperature range from -40°C to 85°C. It is manufactured using the 0.13 µm CMOS process.

Introduction

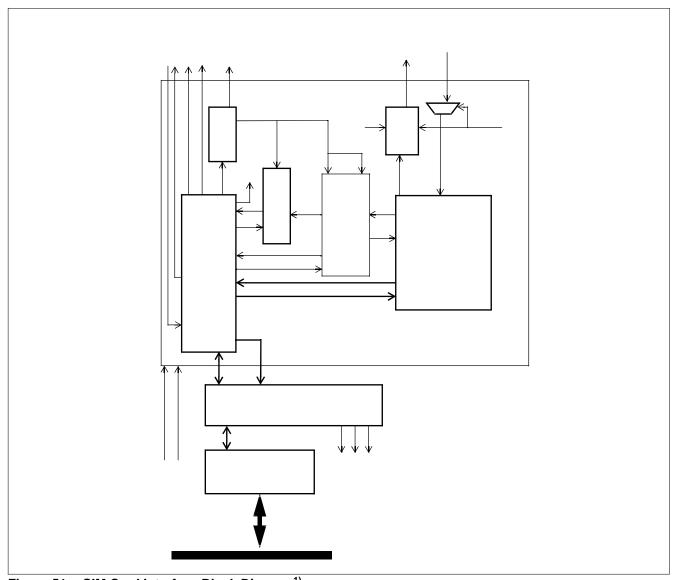

Figure 1 E-GOLDvoice Block Diagram

#### 1.2 Features

#### **Baseband**

- High performance fixed-point TEAKlite DSP

- C166S high performance microcontroller

- There are several Interfaces:

- I2S interface for DAI connections (for Tape Approval)

- High Speed SSC Interface for connection of external peripherals

- SIM Interface

- Keypad Interface (6x4 or 5x5 keys)

- EBU for external RAM/FLASH connection

- Asynchronous serial interface (incl. IrDA support capability)

- JTAG Interface

- Black & white and color displays are supported

- PWM source to drive vibrator

- Keypad and display backlight supported.

#### Receiver

- Constant gain, direct conversion receiver with fully integrated blocking filter

- Two integrated LNAs

- · No need of interstage and IF filter

- Highly linear RF quadrature demodulator

- Programmable DC output level

- · Very low power budget.

#### **Transmitter**

- Digital Sigma-Delta modulator for GMSK modulation, typical -163.5 dBc/Hz @ 20 MHz

- Single ended outputs to PA, Pout = +3.5 dBm

- Very low power budget.

#### **RF-Synthesizer**

- ©—Synthesizer for multi-slot operation

- Fast lock-in times (< 150 ∞s)</li>

- Integrated loop filter

- RF Oscillator

- Fully integrated RF VCO.

#### **Crystal Oscillator**

• Fully digital controlled crystal oscillator core with a highly linear tuning characteristic.

#### Mixed Signal and Power Management Unit

- DC/DC boost for voltages up to 15V for driving White or Blue LEDs

- 8-Ohm loud speaker driver (250/350mW)

- 16-Ohm earpiece driver

- 32-Ohm headset driver

- 4 measurement interfaces (PA temperature, battery voltage, battery temperature, and ambient temperature)

- Differential microphone input

- System start up circuitry

- · Charger circuitry for NiCd, NiMh and Lilon cells

- Integrated regulators for direct connection to battery.

#### **Package**

E-GOLDvoice utilizes an LF2BGA-189-1 lead-free (green) package. The high degree of integration in E-GOLDvoice in conjunction with a sophisticated designed ball-out allows building a complete mobile phone complete with all its peripherals on a 4-layer PCB.

#### 1.3 Application

E-GOLDvoice was developed for very low cost voice-only Dual Band GSM system solutions.

#### 1.4 GSM System Description

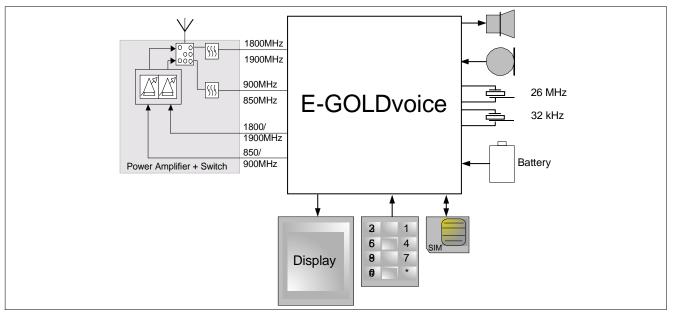

Figure 2 shows a typical application circuit for the E-GOLDvoice.

Figure 2 Typical E-GOLDvoice Application Circuit

The E-GOLDvoice is suited for mobile stations operating in the GSM850/900/1800/1900 bands.

In the receiver path the antenna input signal is converted to the baseband, filtered, and then amplified to target level by the RF transceiver chipset. Two A-to-D converters generate two 6.5 Mbit/s data streams. The decimation and narrowband channel filtering is done by a digital baseband filter in each path. The DSP performs:

- 1. The GMSK equalization of the received baseband signal (SAIC support available)

- 2. Viterbi channel decoding supported by an hardware accelerator.

The recovered digital speech data is fed into the speech decoder. The E-GOLDvoice supports fullrate, halfrate, enhanced fullrate and adaptive multirate speech CODEC algorithms.

Target Specification 23 Rev. 1.05, 2006-12-06

The generated voice signal passes through a digital voiceband filter. The resulting 4 Mbit/s data stream is D-to-A converted by a multi-bit-oversampling converter, postfiltered, and then amplified by a programmable gain stage. The output buffer can drive a handset ear-piece or an external audio amplifier, an additional output driver for external loud speaker is implemented.

In the transmit direction the differential microphone signal is fed into a programmable gain amplifier. The prefiltered and A-to-D converted voice signal forms a 2 Mbit/s data stream. The oversampled voice signal passes a digital decimation filter.

The E-GOLDvoice performs speech and channel encoding (including voice activity detection (VAD) and discontinuous transmission (DTX)) and digital GMSK modulation.

In the RF transceiver part, the baseband signal modulates the RF carrier at the desired frequency in the 850 MHz, 900 MHz, 1.8 GHz, and 1.9 GHz bands using an I/Q modulator. The E-GOLDvoice supports dual band applications.

Finally, an RF power module amplifies the RF transmit signal at the required power level. Using software, the E-GOLDvoice controls the gain of the power amplifier by predefined ramping curves (16 words, 11 bits). For baseband operation, the E-GOLDvoice supports:

- · Making or receiving a voice call

- · Sending or receiving an SMS.

#### 1.5 PMU Details

The E-GOLDvoice includes battery charger support (various sensor connections for temperature, battery technology, voltage, etc.) and a ringer buffer.

E-GOLDvoice avoids the need for an external power management component because its internal power management unit contains:

- Voltage regulators for the On-chip and Off-chip functional blocks

- Charger circuitry for NiCd, NiMh and Lilon cells.

#### 1.6 Bus Concept

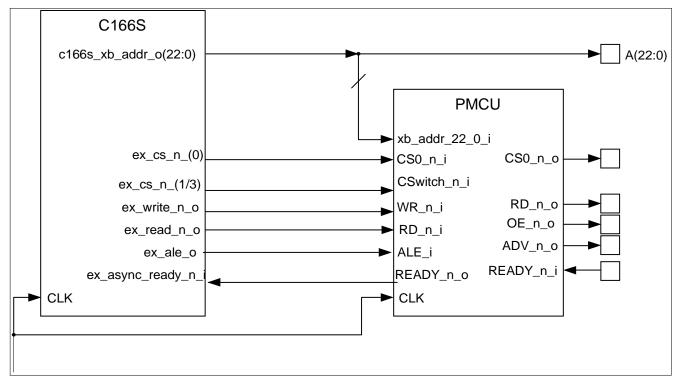

The E-GOLDvoice has two cores (a microcontroller and a DSP), each with its own bus.

There is an interconnection between the TEAKlite bus and the C166S X-Bus.

#### 1.6.1 C166S Buses

The C166S is connected to three buses:

- 1. Local Memory (LM) bus

- 2. X-Bus

- 3. PD-Bus.

#### 1.6.2 TEAKLite Bus

The TEAKlite is connected to the TEAKlite bus.

#### **GSM Cipher Unit**

This unit on the TEAKlite bus calculates the GSM/EDGE encryption keystream and the GSM/EDGE decryption keystream. It implements the following algorithms: A5/1, A5/2, and A5/3.

#### 1.6.3 Bus Interconnections

The interconnection between the X-Bus and the TEAKlite Bus uses:

- Multicore Synchronization

- Shared Memory.

## 1.7 Clock Concept

The E-GOLDvoice has a flexible clock control.

## 1.8 Interrupt Concept

The C166 MCU carries out the E-GOLDvoice interrupt system.

## 1.9 Debug Concept

The E-GOLDvoice includes a multi-core debug. The C166 and TEAKlite cores can be debugged in parallel with:

- A single JTAG port (that is, on a single host)

- · Mutual breakpoint control.

#### 1.9.1 C166 Debug Concept

The debugging of the C166 uses the OCDS and the Cerberus.

#### 1.9.2 TEAKLite Debug Concept

TEAKlite debugging uses the OCEM and the SEIB.

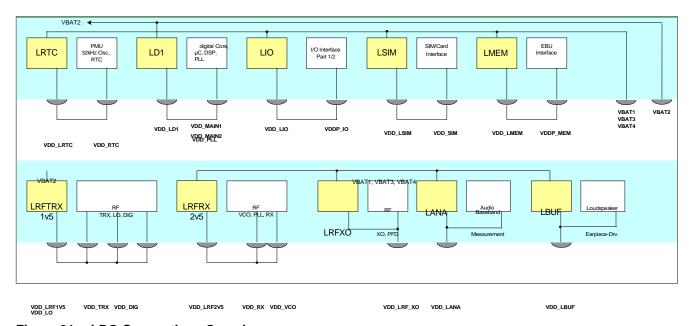

#### 1.10 Power Management

The E-GOLDvoice provides the power management unit (PMU) for the complete mobile phone application. The integrated PMU is directly connected to the battery and provides a set of linear voltage regulators (LDO's). These LDO's generate all required supply voltages and currents needed in a low feature mobile phone.

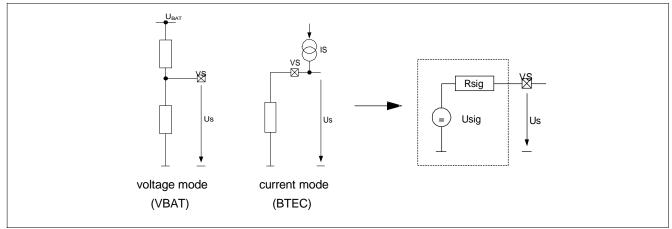

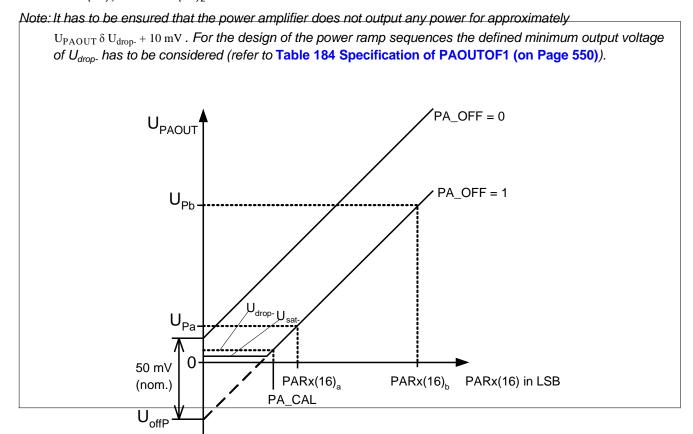

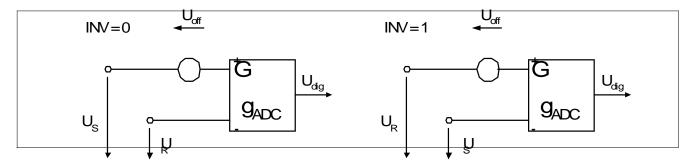

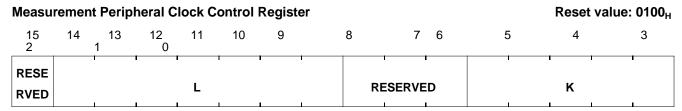

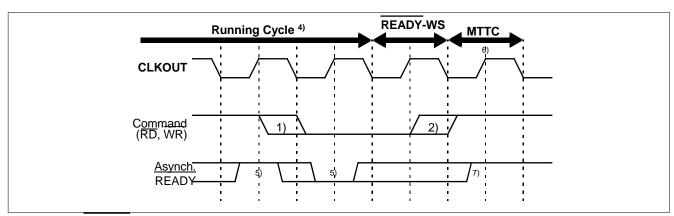

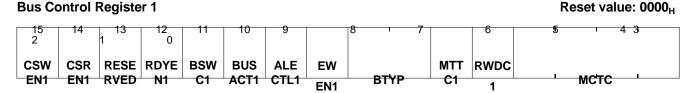

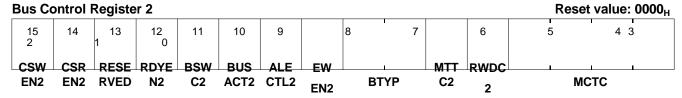

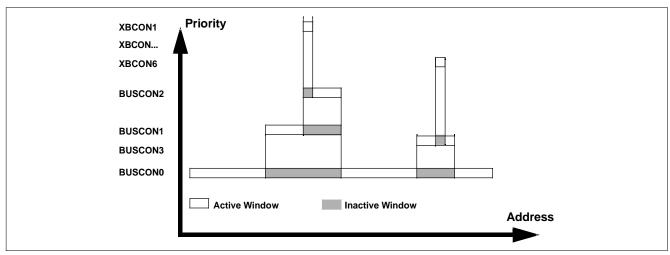

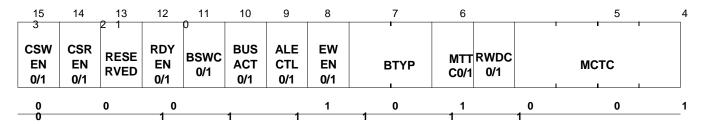

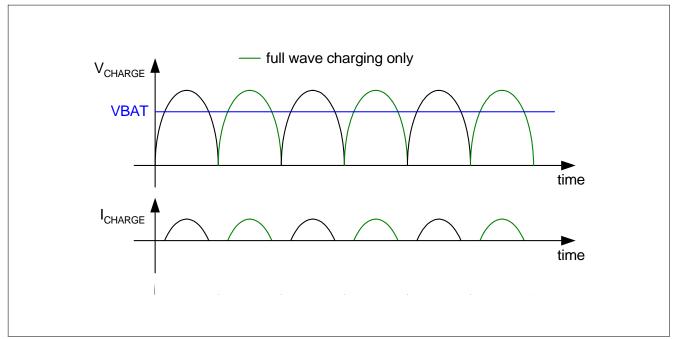

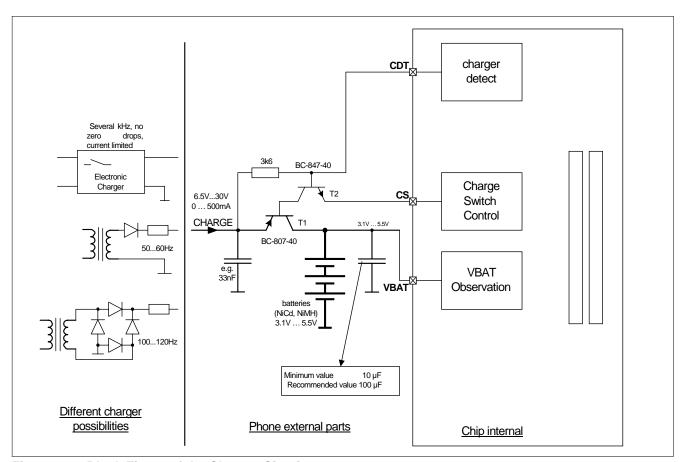

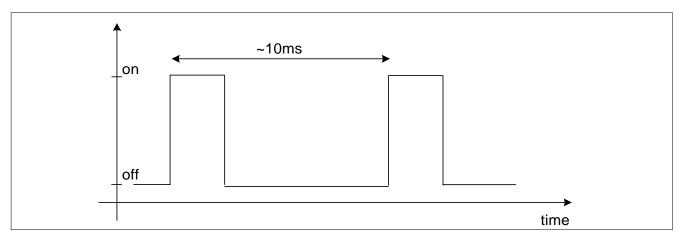

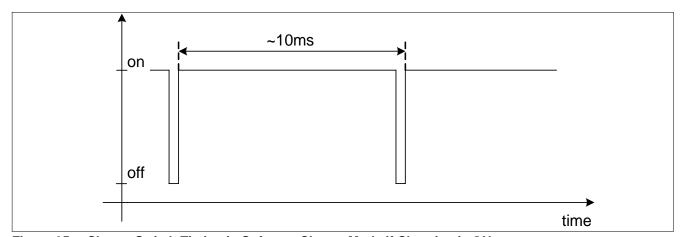

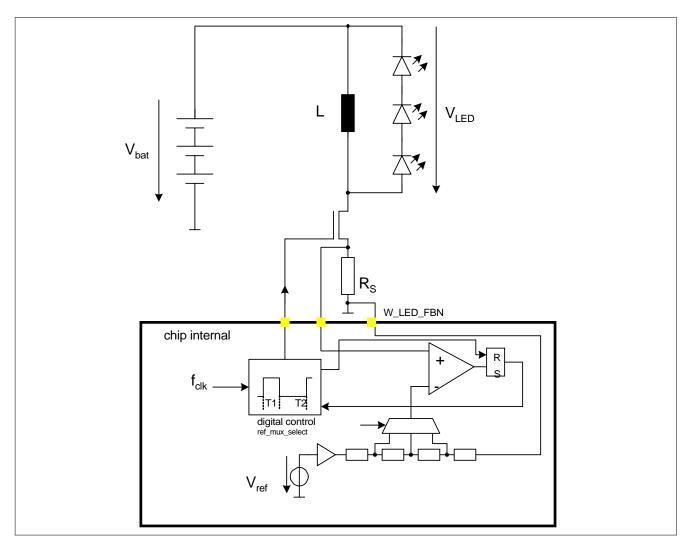

A charger control circuit charges NiCd, NiMH and Lilon batteries. The charger control supports hardware controlled pre-charging and software controlled charging. It offers a wide charger voltage range, making half-wave/full-wave charging with cheap transformers possible.