## MOS 1024-BIT NON-VOLATILE RANDOM ACCESS MEMORY

### MBM2212-20 MBM2212-25

December 1987 Edition 3.0

# 1024-BIT NON-VOLATILE STATIC RANDOM ACCESS MEMORY

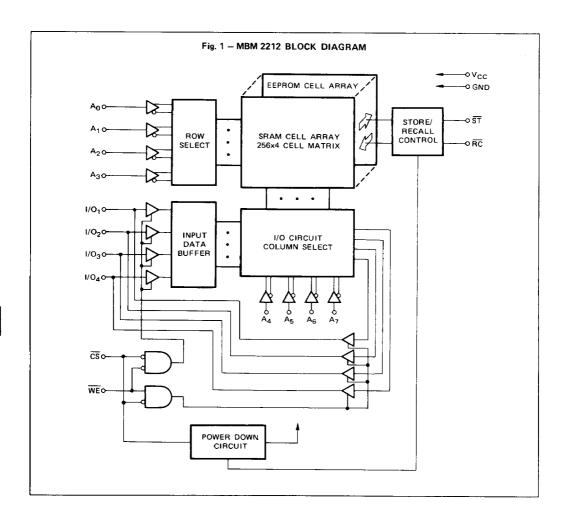

The Fujitsu MBM 2212 is a 1024-bit non-volatile static random access memory (NVRAM) combined 1024 bit static random access memory (SRAM) and electrically erasable programmable read only memory (EEPROM) on one-chip. It is designed for applications such as system potentiometer or electrical switch to memorize the system condition etc.

The MBM 2212 is organized as 256 words by 4 bit. Each one word is constituted with a pair of SRAM and EEPROM cell. The read and write operations are performed on the SRAM cell. The data transfer between SRAM and EEPROM is performed using two control pins. The store mode (transfering SRAM data to EEPROM) is executed with one shot pulse applied to  $\overline{\text{ST}}$  pin in 10ms. The recall mode (transfering EEPROM data to SRAM) is executed with one shot pulse applied to  $\overline{\text{RC}}$  pin in 1.2 $\mu$ s. Both store and recall operations are completed all bits at one time.

The MBM 2212 is fabricated using N-MOS silicon gate technology with floating gate cells. Single +5V supply and TTL input/output level operations greatly facilitate microprocessor applications.

- 256 words x 4 bit organization, fully decoded

- 10ms self-timed auto store

- 10 years data retention for each store

- Unlimited endurance for recall

- TTL compatible inputs/outputs

- Tri-state output

- Write protection on power-on/off and surge pulse

- Low power consumption; Active: 330mW max.

Standby: 165mW max.

- · Fast access time:

200ns max. (MBM 2212-20) 250ns max. (MBM 2212-25)

Standard 18 pin CERAMIC DIP package: Suffix-Z

Standard 18 pin PLASTIC DIP package: Suffix-P

Pin compatible with Xicor X2212

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating                                       | Symbol                             | Value        | Unit |

|----------------------------------------------|------------------------------------|--------------|------|

| Supply Voltage with Respect to GND           | V <sub>cc</sub>                    | -1.0 to +7.0 | V    |

| All Input/Output Voltage with Respect to GND | V <sub>IN</sub> , V <sub>OUT</sub> | -1.0 to +7.0 | ٧    |

| Output Current with Respect to GND           | lout                               | +5.0         | mA   |

| Temperature under Bias                       | T <sub>BIAS</sub>                  | -10 to +85   | °C   |

| Storage Temperature                          | T <sub>STG</sub>                   | -65 to +125  | °c   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

## CAPACITANCE (TA = 25°C, f = 1 MHz)

| Parameter                                | Symbol           | Min | Тур | Max | Unit |

|------------------------------------------|------------------|-----|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> = 0V) | C <sub>IN</sub>  |     |     | 6   | ρF   |

| I/O Capacitance (V <sub>I/O</sub> = 0V)  | C <sub>I/O</sub> |     |     | 8   | pF   |

### TRUTH TABLE

| MODE    | CS              | WE              | RC              | ST              | 1/0              | V <sub>cc</sub> | GND | POWER        |

|---------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----|--------------|

| Standby | V <sub>IH</sub> | ×               | V <sub>IH</sub> | V <sub>IH</sub> | High-Z           | 5V              | GND | Standby      |

| Read    | VIL             | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | D <sub>out</sub> | 5V              | GND | Active       |

| Write   | VIL             | VIL             | V <sub>IH</sub> | V <sub>IH</sub> | D <sub>IN</sub>  | 5V              | GND | Active       |

| Recall  | x               | V <sub>IH</sub> | .,              | .,              | 11: 7            | EV              | CND | Constitution |

| Recail  | V <sub>IH</sub> | ×               | V <sub>IL</sub> | V <sub>IH</sub> | High-Z           | 5V              | GNÐ | Standby      |

| Store   | ×               | V <sub>IH</sub> |                 | .,              | Lligh 7          | EV              | CND | A =4:=       |

| Store   | V <sub>IH</sub> | ×               | V <sub>IH</sub> | V <sub>IL</sub> | High-Z           | gh-Z 5V         | GND | Active       |

Note: X Can be either  $V_{IL}$  or  $V_{IH}$

### RECOMMENDED OPERATING CONDITIONS

(Referenced to GND)

| Parameter             | Symbol          | Min   | Тур | Max                  | Unit |

|-----------------------|-----------------|-------|-----|----------------------|------|

| Supply Voltae         | V <sub>cc</sub> | 4.5   | 5.0 | 5.5                  | ٧    |

| Input High Level      | V <sub>IH</sub> | 2.0   |     | V <sub>cc</sub> +0.5 | ٧    |

| Input Low Level       | V <sub>IL</sub> | -1.0* |     | 8.0                  | V    |

| Operating Temperature | TA              | 0     |     | 70                   | °C   |

Note: \* For less than 50ns undershoot, but -0.5V for DC.

### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                             | Condition                                                                          | Symbol             | Min | Max | Unit |

|---------------------------------------|------------------------------------------------------------------------------------|--------------------|-----|-----|------|

| Input Leakage Current                 | V <sub>IN</sub> = GND to 5.5V                                                      | Hull               |     | 10  | μА   |

| I/O Leakage Current                   | $\overline{CS} = V_{1H}$ , $V_{1/O} = GND$ to 5.5V                                 | II <sub>LO</sub> I |     | 10  | μА   |

| V <sub>CC</sub> Standby Current       | $\overline{CS} = V_{IH}$ , $V_{CC} = 4.5V$ to 5.5V, $I_{I/O} = 0$ mA <sup>*1</sup> | I <sub>SB</sub>    |     | 30  | mA   |

| V <sub>CC</sub> Active Current        | $\overline{\text{CS}} = V_{1L}, V_{CC} = 5.5V, I_{1/O} = 0\text{mA}^{*2}$          | 1 <sub>cc</sub>    |     | 60  | mA   |

| Output Low Level                      | I <sub>OL</sub> = 4.2mA                                                            | VoL                |     | 0.4 | V    |

| Output High Level                     | I <sub>OH</sub> = -2.0mA                                                           | V <sub>OH</sub>    | 2.4 |     | V    |

| Store Inhibit V <sub>CC</sub> Voltage |                                                                                    | V <sub>IHBT</sub>  |     | 2.7 | V    |

Note: \*1 Supply current increases to I<sub>CC</sub> while store mode regardless of  $\overline{CS}$  level.

\*2 Supply current reduces to I<sub>SB</sub> while recall mode regardless of  $\overline{CS}$  level.

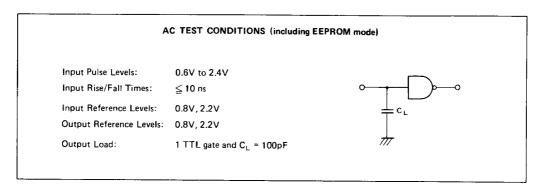

## **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

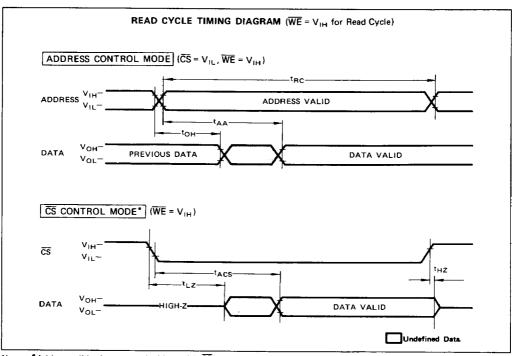

READ MODE (WE = ST = RC = VH)

| Parameter                        | Cumb at          | MBM 2212-20 |     | MBM 2212-25 |     |      |

|----------------------------------|------------------|-------------|-----|-------------|-----|------|

| rarameter                        | Symbol           | Min         | Max | Min         | Max | Unit |

| Read Cycle Time                  | t <sub>RC</sub>  | 200         |     | 250         |     | ns   |

| Address Access Time              | t <sub>AA</sub>  |             | 200 |             | 250 | ns   |

| Chip Select Access Time          | t <sub>ACS</sub> |             | 200 |             | 250 | ns   |

| Output Hold after Address Change | t <sub>OH</sub>  | 50          | -   | 50          |     | ns   |

| Chip Select to Output Active*    | t <sub>LZ</sub>  | 10          |     | 10          |     | ns   |

| Chip Select to Output Disable*   | t <sub>HZ</sub>  |             | 100 |             | 100 | ns   |

Note: \* Transition is measured at point of ±500mV from steady state voltage.

Note: \*Address valid prior to or coincident with CS transition low.

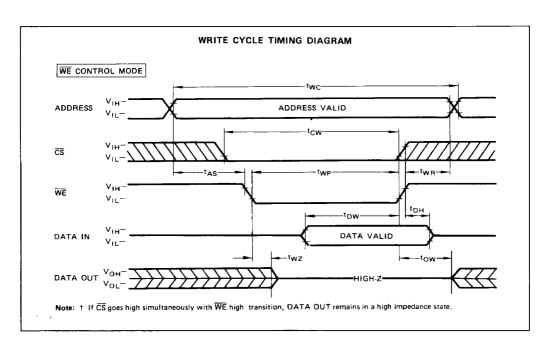

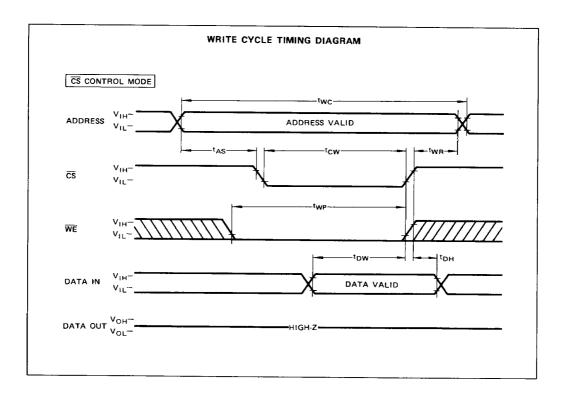

#### WRITE MODE (ST = RC = VIH)

| <b>P</b>                                  | 0               | MBM 22 |     |      |

|-------------------------------------------|-----------------|--------|-----|------|

| Parameter                                 | Symbol          | Min    | Max | Unit |

| Write Cycle Time                          | twc             | 300    |     | ns   |

| Chip Select to End of Write (WE = VIL)    | tcw             | 150    |     | ns   |

| Address Setup Time                        | t <sub>AS</sub> | 50     |     | ns   |

| Write Pulse Width (CS = V <sub>1L</sub> ) | t <sub>WP</sub> | 150    |     | ns   |

| Write Recovery Time*1                     | twn             | 25     |     | ns   |

| Data Valid to End of Write                | t <sub>DW</sub> | 100    |     | ns   |

| Data Hold Time                            | t <sub>DH</sub> | 0      |     | ns   |

| Write Enable to Output High-Z*2           | t <sub>wz</sub> |        | 100 | ns   |

| Output Active from End of Write*3         | tow             | 10     |     | ns   |

Note: \*1  $t_{WR}$  is defined from the end point of write.

- \*2 Transition is measured at point of ±500mV from steady state voltage.

- \*3 If  $\overline{\text{CS}}$  goes high coincident with  $\overline{\text{WE}}$  high transition, DATA OUT remains in a high impedance state.

#### **EEPROM READ/WRITE INFORMATION**

The MBM 2212 can not read or write EEPROM data externally and it must be transferred from/to SRAM cell array corresponding to each EEPROM bit. RC and ST pins are assigned to execute these operation easily.

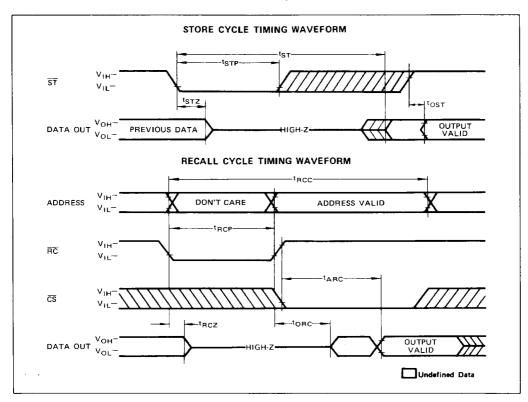

#### RECALL MODE

The recall mode is initiated when negative pulse ( $\square \Gamma$ ) is applied to  $\overline{RC}$  pin while either  $\overline{CS} = V_{IH}$  or  $\overline{WE} = V_{IH}$  and is completed within 1.2 $\mu$ s. The supply current is reduced to standby current automatically.

Please notice that the SRAM data is replaced by the EEPROM data after the execution of this operation.

#### STORE MODE

The store mode is initiated when negative pulse ( $\square$ ) is applied to  $\overline{ST}$  pin while either  $\overline{CS} = V_{IH}$  or  $\overline{WE} = V_{IH}$  and is completed automatically be the on-chip timer. During this operation mode, all input and output pins are inhibited. The original SRAM data remains after the store mode.

The MBM 2212 has two protection circuits to prevent a erroneous store mode. Noise filter circuit for duration of less than 20ns negative pulse on  $\overline{ST}$  pin is on the chip.

Auto-standby circuit prevents the store data on the EEPROM cell array from the destruction when V<sub>CC</sub> is less than +3V.

When  $V_{CC}$  power is ON or OFF, the  $V_{IH}$  input level must be applied to  $\overline{ST}$  pin before or while  $V_{CC}$  is greater than +3V.

These operation modes as store mode, recall mode and SRAM write mode have the same logical priority. Normally the first set logical condition determines the following operation mode among ST, RC and WE pins.

## **EEPROM READ/WRITE INFORMATION (cont'd)**

### **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

RECALL MODE (WE = ST = VIH)

| Parameter             | Combal           | MBM 22 |     |      |

|-----------------------|------------------|--------|-----|------|

| Farameter             | Symbol           | Min    | Max | Unit |

| Recall Cycle Time     | <sup>†</sup> RCC | 1200   |     | ns   |

| Recall Pulse Width    | t <sub>RCP</sub> | 450    |     | ns   |

| RC to Output Disable* | <sup>†</sup> RCZ |        | 150 | ns   |

| RC to Output Active*  | t <sub>ORC</sub> | 10     |     | ns   |

| RC to Output Valid    | tARC             |        | 750 | ns   |

Note: \* Transition is measured at point of ±500mV from steady state voltage.

#### STORE MODE (WE = RC = VIH)

| Parameter                      | Symbol           | МВМ | 2212-20 | мвм | 2212-25 | Unit   |

|--------------------------------|------------------|-----|---------|-----|---------|--------|

| r arameter                     | Jymbor           | Min | Max     | Min | Max     | 1 Unit |

| Store Cycle Time               | t <sub>ST</sub>  |     | 10      |     | 20      | ms     |

| Store Pulse Width*1            | t <sub>STP</sub> | 100 |         | 100 |         | ns     |

| Store to Output Disable*2      | t <sub>STZ</sub> |     | 500     |     | 500     | ns     |

| Output Valid from End of Store | t <sub>OST</sub> |     | 200     |     | 250     | ns     |

Note: \*1 It is protected to enter into the store mode by less than 20ns pulse width.

\*2 Transition is measured at point of ±500mV from steady state voltage.

#### **ENDURANCE**

| Number of Store Cycles | Number of Data Changes per Bit | Unit  |

|------------------------|--------------------------------|-------|

| 100,000                | 10,000                         | times |

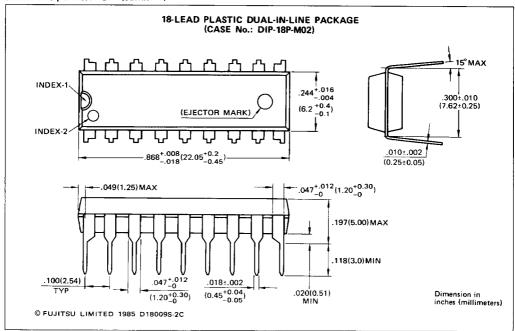

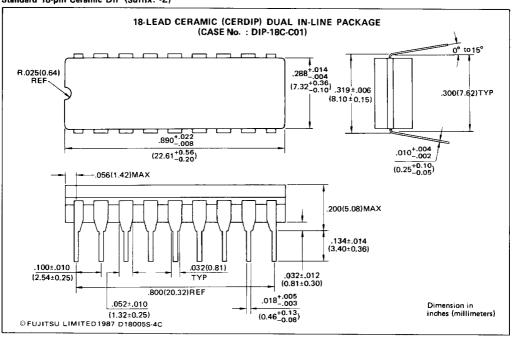

### PACKAGE DIMENSIONS

Standard 18-pin Ceramic DIP (Suffix: -Z)

### **PACKAGE DIMENSIONS**

Standard 18-pin Plastic DIP (Suffix: -P)